MC9S12C128CFUE Freescale Semiconductor, MC9S12C128CFUE Datasheet - Page 220

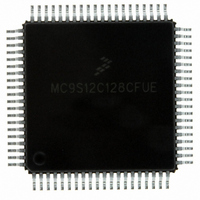

MC9S12C128CFUE

Manufacturer Part Number

MC9S12C128CFUE

Description

IC MCU 128K FLASH 25MHZ 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Specifications of MC9S12C128CFUE

Core Processor

HCS12

Core Size

16-Bit

Speed

25MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

60

Program Memory Size

128KB (128K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Cpu Family

HCS12

Device Core Size

16b

Frequency (max)

25MHz

Interface Type

CAN/SCI/SPI

Total Internal Ram Size

4KB

# I/os (max)

60

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

2.5/5V

Operating Supply Voltage (max)

2.75/5.5V

Operating Supply Voltage (min)

2.35/2.97V

On-chip Adc

8-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

80

Package Type

PQFP

Processor Series

S12C

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

4000 B

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

61

Number Of Timers

1

Operating Supply Voltage

- 0.3 V to + 6.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

M68EVB912C32EE

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12C128CFUE

Manufacturer:

ST

Quantity:

6 246

Company:

Part Number:

MC9S12C128CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 220 of 690

- Download datasheet (4Mb)

Chapter 7 Debug Module (DBGV1) Block Description

7.4.2.6.3

In the detail mode, address and data for all cycles except program fetch (P) and free (f) cycles are stored

in trace buffer. This mode is intended to supply additional information on indexed, indirect addressing

modes where storing only the destination address would not provide all information required for a user to

determine where his code was in error.

7.4.2.6.4

This mode is intended to allow a host computer to poll a running target and provide a histogram of program

execution. Each read of the trace buffer address will return the address of the last instruction executed. The

DBGCNT register is not incremented and the trace buffer does not get filled. The ARM bit is not used and

all breakpoints and all other debug functions will be disabled.

7.4.2.7

The storage memory is a 64 words deep by 16-bits wide dual port RAM array. The CPU accesses the RAM

array through a single memory location window (DBGTBH:DBGTBL). The DBG module stores trace

information in the RAM array in a circular buffer format. As data is read via the CPU, a pointer into the

RAM will increment so that the next CPU read will receive fresh information. In all trigger modes except

for event-only and detail capture mode, the data stored in the trace buffer will be change-of-flow addresses.

change-of-flow addresses are defined as follows:

In the event-only trigger modes only the 16-bit data bus value corresponding to the event is stored. In the

detail capture mode, address and then data are stored for all cycles except program fetch (P) and free (f)

cycles.

7.4.2.8

7.4.2.8.1

Storing with begin-trigger can be used in all trigger modes. When DBG mode is enabled and armed in the

begin-trigger mode, data is not stored in the trace buffer until the trigger condition is met. As soon as the

trigger condition is met, the DBG module will remain armed until 64 words are stored in the trace buffer.

If the trigger is at the address of the change-of-flow instruction the change-of-flow associated with the

trigger event will be stored in the trace buffer.

7.4.2.8.2

Storing with end-trigger cannot be used in event-only trigger modes. When DBG mode is enabled and

armed in the end-trigger mode, data is stored in the trace buffer until the trigger condition is met. When

the trigger condition is met, the DBG module will become de-armed and no more data will be stored. If

220

•

•

•

•

Source address of conditional branches (long, short, BRSET, and loop constructs) taken

Destination address of indexed JMP, JSR, and CALL instruction

Destination address of RTI, RTS, and RTC instructions

Vector address of interrupts except for SWI and BDM vectors

Storage Memory

Storing Data in Memory Storage Buffer

Detail Mode

Profile Mode

Storing with Begin-Trigger

Storing with End-Trigger

MC9S12C-Family / MC9S12GC-Family

Rev 01.24

Freescale Semiconductor

Related parts for MC9S12C128CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: