MC9S12C64CFUE Freescale Semiconductor, MC9S12C64CFUE Datasheet - Page 193

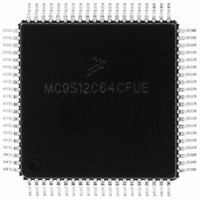

MC9S12C64CFUE

Manufacturer Part Number

MC9S12C64CFUE

Description

IC MCU 64K FLASH 4K RAM 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Specifications of MC9S12C64CFUE

Core Processor

HCS12

Core Size

16-Bit

Speed

25MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

60

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Processor Series

S12C

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

4 KB

Interface Type

CAN/SCI/SPI

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

60

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

M68EVB912C32EE

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Package

80PQFP

Family Name

HCS12

Maximum Speed

25 MHz

Operating Supply Voltage

2.5|5 V

Height

2.4 mm

Length

14 mm

Supply Voltage (max)

2.75 V, 5.5 V

Supply Voltage (min)

2.35 V, 2.97 V

Width

14 mm

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12C64CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 193 of 690

- Download datasheet (4Mb)

7.1.2

There are two main modes of operation: breakpoint mode and debug mode. Each one is mutually exclusive

of the other and selected via a software programmable control bit.

In the breakpoint mode there are two sub-modes of operation:

In debug mode, there are several sub-modes of operation.

7.1.3

Figure 7-1

module in debug mode.

Freescale Semiconductor

•

•

•

•

— Data associated with event B trigger modes

— Detail report mode stores address and data for all cycles except program (P) and free (f) cycles

— Current instruction address when in profiling mode

— BGND is not considered a change-of-flow (cof) by the debugger

Dual address mode, where a match on either of two addresses will cause the system to enter

background debug mode (BDM) or initiate a software interrupt (SWI).

Full breakpoint mode, where a match on address and data will cause the system to enter

background debug mode (BDM) or initiate a software interrupt (SWI).

Trigger modes

There are many ways to create a logical trigger. The trigger can be used to capture bus information

either starting from the trigger or ending at the trigger. Types of triggers (A and B are registers):

— A only

— A or B

— A then B

— Event only B (data capture)

— A then event only B (data capture)

— A and B, full mode

— A and not B, full mode

— Inside range

— Outside range

Capture modes

There are several capture modes. These determine which bus information is saved and which is

ignored.

— Normal: save change-of-flow program fetches

— Loop1: save change-of-flow program fetches, ignoring duplicates

— Detail: save all bus operations except program and free cycles

— Profile: poll target from external device

is a block diagram of this module in breakpoint mode.

Modes of Operation

Block Diagram

MC9S12C-Family / MC9S12GC-Family

Rev 01.24

Chapter 7 Debug Module (DBGV1) Block Description

Figure 7-2

is a block diagram of this

193

Related parts for MC9S12C64CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: