MC9S12C64CFUE Freescale Semiconductor, MC9S12C64CFUE Datasheet - Page 595

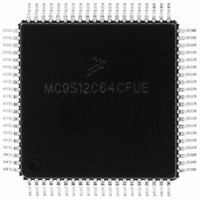

MC9S12C64CFUE

Manufacturer Part Number

MC9S12C64CFUE

Description

IC MCU 64K FLASH 4K RAM 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Specifications of MC9S12C64CFUE

Core Processor

HCS12

Core Size

16-Bit

Speed

25MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

60

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Processor Series

S12C

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

4 KB

Interface Type

CAN/SCI/SPI

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

60

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

M68EVB912C32EE

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Package

80PQFP

Family Name

HCS12

Maximum Speed

25 MHz

Operating Supply Voltage

2.5|5 V

Height

2.4 mm

Length

14 mm

Supply Voltage (max)

2.75 V, 5.5 V

Supply Voltage (min)

2.35 V, 2.97 V

Width

14 mm

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12C64CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 595 of 690

- Download datasheet (4Mb)

All bits read 0 and are not writable.

20.4

20.4.1

Write operations are used for the program, erase, and erase verify algorithms described in this section. The

program and erase algorithms are controlled by a state machine whose timebase FCLK is derived from the

oscillator clock via a programmable divider. The FCMD register as well as the associated FADDR and

FDATA registers operate as a buffer and a register (2-stage FIFO) so that a new command along with the

necessary data and address can be stored to the buffer while the previous command is still in progress. This

pipelined operation allows a time optimization when programming more than one word on a specific row,

as the high voltage generation can be kept active in between two programming commands. The pipelined

operation also allows a simplification of command launching. Buffer empty as well as command

completion are signalled by flags in the FSTAT register with corresponding interrupts generated, if

enabled.

The next sections describe:

20.4.1.1

Prior to issuing any Flash command after a reset, it is first necessary to write the FCLKDIV register to

divide the oscillator clock down to within the 150-kHz to 200-kHz range. Since the program and erase

timings are also a function of the bus clock, the FCLKDIV determination must take this information into

account.

If we define:

Freescale Semiconductor

Module Base + 0x000F

Reset

•

•

•

•

•

•

•

W

R

How to write the FCLKDIV register

Command write sequence used to program, erase or erase verify the Flash array

Valid Flash commands

Errors resulting from illegal Flash operations

FCLK as the clock of the Flash timing control block

Tbus as the period of the bus clock

INT(x) as taking the integer part of x (e.g., INT(4.323) = 4),

Functional Description

Flash Command Operations

Writing the FCLKDIV Register

0

0

7

= Unimplemented or Reserved

0

0

6

MC9S12C-Family / MC9S12GC-Family

0

0

5

Figure 20-22. RESERVED6

Rev 01.24

0

0

4

0

0

3

Chapter 20 96 Kbyte Flash Module (S12FTS96KV1)

0

0

2

0

0

1

0

0

0

595

Related parts for MC9S12C64CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: