ATTINY48-PU Atmel, ATTINY48-PU Datasheet - Page 97

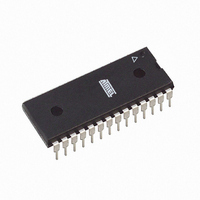

ATTINY48-PU

Manufacturer Part Number

ATTINY48-PU

Description

MCU AVR 4K ISP FLASH 1.8V 28-DIP

Manufacturer

Atmel

Series

AVR® ATtinyr

Specifications of ATTINY48-PU

Core Processor

AVR

Core Size

8-Bit

Speed

12MHz

Connectivity

I²C, SPI

Peripherals

Brown-out Detect/Reset, POR, WDT

Number Of I /o

24

Program Memory Size

4KB (2K x 16)

Program Memory Type

FLASH

Eeprom Size

64 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 6x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-DIP (0.300", 7.62mm)

Processor Series

ATTINY4x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

2-Wire/I2S/SPI

Maximum Clock Frequency

12 MHz

Number Of Programmable I/os

28

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT

Minimum Operating Temperature

- 40 C

On-chip Adc

6-ch x 10-bit

Package

28PDIP

Device Core

AVR

Family Name

ATtiny

Maximum Speed

12 MHz

Operating Supply Voltage

2.5|3.3|5 V

For Use With

ATSTK600 - DEV KIT FOR AVR/AVR32ATAVRDRAGON - KIT DRAGON 32KB FLASH MEM AVRATAVRISP2 - PROGRAMMER AVR IN SYSTEM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATTINY48-PU

Manufacturer:

ATMEL

Quantity:

5 530

Company:

Part Number:

ATTINY48-PU

Manufacturer:

AVX

Quantity:

30 000

- Current page: 97 of 302

- Download datasheet (9Mb)

12.7

8008G–AVR–04/11

Output Compare Units

Using the Input Capture unit in any mode of operation when the TOP value (resolution) is

actively changed during operation, is not recommended.

Measurement of an external signal’s duty cycle requires that the trigger edge is changed after

each capture. Changing the edge sensing must be done as early as possible after the ICR1

Register has been read. After a change of the edge, the Input Capture Flag (ICF1) must be

cleared by software (writing a logical one to the I/O bit location). For measuring frequency only,

the clearing of the ICF1 Flag is not required (if an interrupt handler is used).

The 16-bit comparator continuously compares TCNT1 with the Output Compare Register

(OCR1x). If TCNT equals OCR1x the comparator signals a match. A match will set the Output

Compare Flag (OCF1x) at the next timer clock cycle. If enabled (OCIE1x = 1), the Output Com-

pare Flag generates an Output Compare interrupt. The OCF1x Flag is automatically cleared

when the interrupt is executed. Alternatively the OCF1x Flag can be cleared by software by writ-

ing a logical one to its I/O bit location. The Waveform Generator uses the match signal to

generate an output according to operating mode set by the Waveform Generation mode

(WGM1[3:0]) bits and Compare Output mode (COM1x[1:0]) bits. The TOP and BOTTOM signals

are used by the Waveform Generator for handling the special cases of the extreme values in

some modes of operation

A special feature of Output Compare unit A allows it to define the Timer/Counter TOP value (i.e.,

counter resolution). In addition to the counter resolution, the TOP value defines the period time

for waveforms generated by the Waveform Generator.

Figure 12-4

bit names indicates the device number (n = 1 for Timer/Counter 1), and the “x” indicates Output

Compare unit (A/B). The elements of the block diagram that are not directly a part of the Output

Compare unit are gray shaded.

Figure 12-4. Output Compare Unit, Block Diagram

shows a block diagram of the Output Compare unit. The small “n” in the register and

OCRnxH Buf. (8-bit)

(See “Modes of Operation” on page

OCRnxH (8-bit)

BOTTOM

OCRnx

TEMP (8-bit)

TOP

OCRnx (16-bit Register)

Buffer (16-bit Register)

OCRnxL Buf. (8-bit)

OCRnxL (8-bit)

DATA BUS

Waveform Generator

WGMn[3:0]

=

(16-bit Comparator )

(8-bit)

COMnx[1:0]

TCNTnH (8-bit)

OCFnx (Int.Req.)

100.)

TCNTn (16-bit Counter)

ATtiny48/88

TCNTnL (8-bit)

OCnx

97

Related parts for ATTINY48-PU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Microcontrollers (MCU) 512B FL 32B SRAM TIMER ATTINY4 12MHz

Manufacturer:

Atmel

Part Number:

Description:

IC MCU AVR 512B FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 512B FLASH SOT-23-6

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC, MCU, 8BIT, 2K FLASH, 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC, MCU, 8BIT, 2K FLASH, 20PDIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC, MCU, 8BIT, 8K FLASH, 20PDIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC, MCU, 8BIT, 8K FLASH, 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet: