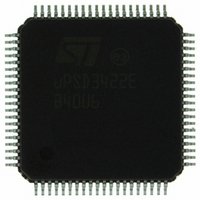

UPSD3422E-40U6 STMicroelectronics, UPSD3422E-40U6 Datasheet - Page 133

UPSD3422E-40U6

Manufacturer Part Number

UPSD3422E-40U6

Description

MCU 8BIT 8032 64KB FLASH 80TQFP

Manufacturer

STMicroelectronics

Series

µPSDr

Datasheet

1.UPSD3422EV-40U6.pdf

(300 pages)

Specifications of UPSD3422E-40U6

Core Processor

8032

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IrDA, SPI, UART/USART, USB

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

46

Program Memory Size

80KB (80K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-TQFP, 80-VQFP

For Use With

497-5577 - BOARD EVAL USB POWER SWITCH497-5518 - EVAL BOARD RFID READER

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Other names

497-4903

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPSD3422E-40U6

Manufacturer:

STMicroelectronics

Quantity:

10 000

- Current page: 133 of 300

- Download datasheet (3Mb)

UPSD3422, UPSD3433, UPSD3434, UPSD3454

23.12

I

The S1SETUP register

will be sampled before the SIOE validates the Start condition, giving the SIOE the ability to

reject noise or illegal transmissions.

Because the minimum duration of an Start condition varies with I

also because the UPSD34xx may be operated with a wide variety of frequencies (f

necessary to scale the number of samples per Start condition based on f

In Slave mode, the SIOE recognizes the beginning of a Start condition when it detects a '1'-

to-'0' transition on the SDA bus line while the SCL line is high (see

The SIOE must then validate the Start condition by sampling the bus lines to ensure SDA

remains low and SCL remains high for a minimum amount of hold time, t

validated, the SIOE begins receiving the address byte that follows the Start condition.

If the EN_SS Bit (in the S1SETUP register) is not set, then the SIOE will sample only once

after detecting the '1'-to-'0' transition on SDA. This single sample is taken 1/f

after the initial 1-to-0 transition was detected. However, more samples should be taken to

ensure there is a valid Start condition.

To take more samples, the SIOE should be initialized such that the EN_SS Bit is set, and a

value is written to the SMPL_SET[6:0] field of the S1SETUP register to specify how many

samples to take. The goal is to take a good number of samples during the minimum Start

condition hold time, t

t

Table 86 on page 134

resulting number of I

on SDA of a Start condition.

Important note: Keep in mind that the time between samples is always 1/f

The minimum Start condition hold time, t

categories per

Table 84.

Table 85.

1. Sampling SCL and SDA lines begins after '1'-to-'0' transition on SDA occurred while SCL is high. Time

HLDSTA

2

6:0

Bit

C Start sample setting (S1SETUP)

EN_SS

7

between samples is 1/f

Bit 7

SMPL_SET

expires.

Symbol

EN_SS

[6:0]

S1SETUP: I

value 00h)

S1SETUP register bit definition

Table 87 on page

Bit 6

2

HLDSTA

R/W

R/W

C bus samples that SIOE will take after detecting the 1-to-0 transition

OSC

describes the relationship between the contents of S1SETUP and the

–

(Table

.

2

C Start condition sample setup register (SFR DBh, reset

Bit 5

, but no so many samples that the bus will be sampled after

Enable Sample Setup

Sample Setting

Specifies the number of bus samples

condition. See

84) determines how many times an I

EN_SS = 1 will force the SIOE to sample

bus the number of times specified in SMPL_SET[6:0].

EN_SS = 0 means the SIOE will sample

one time, regardless of the contents of SMPL_SET[6:0].

134.

Bit 4

HLDSTA

Table 86

SMPL_SET[6:0]

, is different for the three common I

Bit 3

for values.

Function

Bit 2

(1)

2

taken during a Start

C bus speed (f

Figure 41 on page

(1)

2

(1)

C bus Start condition

a Start condition on the

a Start condition only

Bit 1

HLDSTA

OSC

OSC

OSC

.

and f

I

2

. Once

C interface

SCL

seconds

2

OSC

SCL

C speed

Bit 0

), and

133/300

), it is

125).

.

Related parts for UPSD3422E-40U6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Fast Turbo 8032 MCU with USB and Programmable Logic

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

MCU 8BIT 8032 64KB FLASH 52TQFP

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: