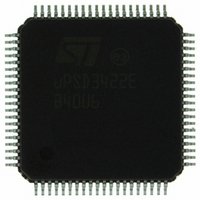

UPSD3422E-40U6 STMicroelectronics, UPSD3422E-40U6 Datasheet - Page 220

UPSD3422E-40U6

Manufacturer Part Number

UPSD3422E-40U6

Description

MCU 8BIT 8032 64KB FLASH 80TQFP

Manufacturer

STMicroelectronics

Series

µPSDr

Datasheet

1.UPSD3422EV-40U6.pdf

(300 pages)

Specifications of UPSD3422E-40U6

Core Processor

8032

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IrDA, SPI, UART/USART, USB

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

46

Program Memory Size

80KB (80K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-TQFP, 80-VQFP

For Use With

497-5577 - BOARD EVAL USB POWER SWITCH497-5518 - EVAL BOARD RFID READER

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Other names

497-4903

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPSD3422E-40U6

Manufacturer:

STMicroelectronics

Quantity:

10 000

- Current page: 220 of 300

- Download datasheet (3Mb)

PSD module

Note:

28.5.26

220/300

The 8032 data bus, D0 - D7, does not route directly to PLD inputs. Instead, the 8032 data

bus has indirect access to the GPLD (not the DPLD) when the 8032 reads and writes the

OMC and IMC registers within csiop address space.

Turbo bit and PLDs

The PLDs can minimize power consumption by going to standby after ALL the PLD inputs

remain unchanged for an extended time (about 70ns). When the Turbo Bit is set to logic one

(Bit 3 of the csiop PMMR0 register), Turbo mode is turned off and then this automatic

standby mode is achieved. Turning off Turbo mode increases propagation delays while

reducing power consumption. The default state of the Turbo Bit is logic zero, meaning Turbo

mode is on. Additionally, four bits are available in the csiop PMMR0 and PMMR2 registers to

block the 8032 bus control signals (RD, WR, PSEN, ALE) from entering the PLDs. This

reduces power consumption and can be used only when these 8032 control signals are not

used in PLD logic equations. See

Table 167. DPLD and GPLD inputs

8032 address bus

8032 bus control signals

Reset from MCU module

Power-Down from Auto-Power Down counter

PortA input macrocells

(80-pin devices only)

PortB input macrocells

PortC input macrocells

Port D inputs

(52-pin devices have only PD1)

Page register

Macrocell OMC bank AB Feedback

Macrocell OMC bank BC Feedback

Flash memory status bit

Input source

Section 28.5.52: Power management on page

UPSD3422, UPSD3433, UPSD3434, UPSD3454

A0-A15

PSEN, RD, WR, ALE

RESET

PA0-PA7

PB0-PB7

PC2, PC3, PC4, PC7

PD1, PD2

PGR0-PGR7

MCELLAB

FB0-7

MCELLBC

FB0-7

Ready/Busy

PDN

Input name

Number of

signals

248.

16

4

1

1

8

8

4

2

8

8

8

1

Related parts for UPSD3422E-40U6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Fast Turbo 8032 MCU with USB and Programmable Logic

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

MCU 8BIT 8032 64KB FLASH 52TQFP

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: