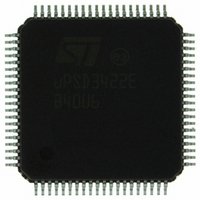

UPSD3422E-40U6 STMicroelectronics, UPSD3422E-40U6 Datasheet - Page 65

UPSD3422E-40U6

Manufacturer Part Number

UPSD3422E-40U6

Description

MCU 8BIT 8032 64KB FLASH 80TQFP

Manufacturer

STMicroelectronics

Series

µPSDr

Datasheet

1.UPSD3422EV-40U6.pdf

(300 pages)

Specifications of UPSD3422E-40U6

Core Processor

8032

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IrDA, SPI, UART/USART, USB

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

46

Program Memory Size

80KB (80K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-TQFP, 80-VQFP

For Use With

497-5577 - BOARD EVAL USB POWER SWITCH497-5518 - EVAL BOARD RFID READER

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Other names

497-4903

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPSD3422E-40U6

Manufacturer:

STMicroelectronics

Quantity:

10 000

- Current page: 65 of 300

- Download datasheet (3Mb)

UPSD3422, UPSD3433, UPSD3434, UPSD3454

13.1.2

13.1.3

13.1.4

13.1.5

13.1.6

13.1.7

13.1.8

Timer 0 and 1 overflow interrupt

Timer 0 and Timer 1 interrupts are generated by the flag bits TF0 and TF1 when there is an

overflow condition in the respective Timer/Counter register (except for Timer 0 in Mode 3).

Timer 2 overflow interrupt

This interrupt is generated to the MCU by a logical OR of flag bits, TF2 and EXE2. The ISR

must read the flag bits to determine the cause of the interrupt.

●

●

UART0 and UART1 interrupt

Each of the UARTs have identical interrupt structure. For each UART, a single interrupt is

generated to the MCU by the logical OR of the flag bits, RI (byte received) and TI (byte

transmitted).

The ISR must read flag bits in the SFR named SCON0 for UART0, or SCON1 for UART1 to

determine the cause of the interrupt.

SPI interrupt

The SPI interrupt has four interrupt sources, which are logically ORed together when

interrupting the MCU. The ISR must read the flag bits to determine the cause of the

interrupt.

A flag bit is set for: end of data transmit (TEISF); data receive overrun (RORISF); transmit

buffer empty (TISF); or receive buffer full (RISF).

I

The flag bit INTR is set by a variety of conditions occurring on the I

own slave address (ADDR flag); received general call address (GC flag); received Stop

condition (STOP flag); or successful transmission or reception of a data byte.The ISR must

read the flag bits to determine the cause of the interrupt.

ADC interrupt

The flag bit AINTF is set when an A-to-D conversion has completed.

PCA interrupt

The PCA has eight interrupt sources, which are logically ORed together when interrupting

the MCU.The ISR must read the flag bits to determine the cause of the interrupt.

●

●

Tables

SFRs.

2

C interrupt

TF2 is set by an overflow of Timer 2.

EXE2 is generated by the falling edge of a signal on the external pin, T2X (pin P1.1).

Each of the six TCMs can generate a "match or capture" interrupt on flag bits OFV5..0

respectively.

Each of the two 16-bit counters can generate an overflow interrupt on flag bits INTF1

and INTF0 respectively.

18

through

Table 24 on page 67

have detailed bit definitions of the interrupt system

2

C interface: received

Interrupt system

65/300

Related parts for UPSD3422E-40U6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Fast Turbo 8032 MCU with USB and Programmable Logic

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

MCU 8BIT 8032 64KB FLASH 52TQFP

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: