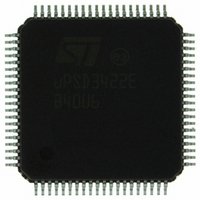

UPSD3422E-40U6 STMicroelectronics, UPSD3422E-40U6 Datasheet - Page 157

UPSD3422E-40U6

Manufacturer Part Number

UPSD3422E-40U6

Description

MCU 8BIT 8032 64KB FLASH 80TQFP

Manufacturer

STMicroelectronics

Series

µPSDr

Datasheet

1.UPSD3422EV-40U6.pdf

(300 pages)

Specifications of UPSD3422E-40U6

Core Processor

8032

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IrDA, SPI, UART/USART, USB

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

46

Program Memory Size

80KB (80K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-TQFP, 80-VQFP

For Use With

497-5577 - BOARD EVAL USB POWER SWITCH497-5518 - EVAL BOARD RFID READER

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Other names

497-4903

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPSD3422E-40U6

Manufacturer:

STMicroelectronics

Quantity:

10 000

- Current page: 157 of 300

- Download datasheet (3Mb)

UPSD3422, UPSD3433, UPSD3434, UPSD3454

25.3.3

Note:

Table 98.

FIFO pairing

The FIFOs on endpoints 1 through 4 may be used independently as shown in

FIFOs with no Pairing or they may be selectively paired to provide double buffering (see

Figure 54 on page

rates with bulk transfers. Double buffering allows the CPU to process a data packet for an

Endpoint while the SIE is receiving or transmitting another packet of data on the same

Endpoint and direction. FIFO pairing is controlled by the USB pairing control register (see

UPAIR,

●

●

●

●

When the FIFOs are paired, the CPU must access the odd numbered FIFO while the even

numbered FIFOs are no longer available for use. Also when they are paired, the active FIFO

is automatically toggled by the update of USIZE.

●

Endpoint

IN FIFO 1 and 2

OUT FIFO 1 and 2

IN FIFO 3 and 4

OUT FIFO 3 and 4

Non-pairing FIFOs Example

Consider a case where the device needs to send 1024 bytes of data to the host.

Without FIFO pairing (see

bytes of data and waits until the host sends an IN token to Endpoint0, and the SIE

transfers the data to the host. Once all 64 bytes have been transferred by the SIE, the

FIFO becomes empty and the CPU starts writing the next 64 bytes of data to the FIFO.

While the CPU is writing the data to the FIFO, the host is sending IN tokens to

Endpoint0, requesting the next 64 bytes of data, but only gets NAKs while the FIFO is

being loaded. Once the FIFO has been loaded by the CPU, the SIE starts sending the

data to the host with the next IN Endpoint0 token. Again, the CPU waits until the SIE

transfers the 64 bytes of data to the host. This is repeated until all 1024 bytes have

been transferred.

0

0

1

1

2

2

3

3

4

4

Table 102 on page

Control

Control

Bulk/Interrupt OUT

Bulk/Interrupt IN

Bulk/Interrupt OUT

Bulk/Interrupt IN

Bulk/Interrupt OUT

Bulk/Interrupt IN

Bulk/Interrupt OUT

Bulk/Interrupt In

UPSD34xx supported endpoints

159). Double buffering provides an efficient way to optimize data transfer

Function

162). FIFO pairing options are listed below:

Figure

53), the CPU loads the IN Endpoint0 FIFO with 64

Max packet size (FIFO

64 bytes

64 bytes

64 bytes

64 bytes

64 bytes

64 bytes

64 bytes

64 bytes

64 bytes

64 bytes

size)

Supported directions

OUT

OUT

OUT

OUT

OUT

USB interface

IN

IN

IN

IN

IN

Figure 53

157/300

as

Related parts for UPSD3422E-40U6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Fast Turbo 8032 MCU with USB and Programmable Logic

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

MCU 8BIT 8032 64KB FLASH 52TQFP

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: