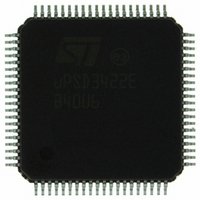

UPSD3422E-40U6 STMicroelectronics, UPSD3422E-40U6 Datasheet - Page 256

UPSD3422E-40U6

Manufacturer Part Number

UPSD3422E-40U6

Description

MCU 8BIT 8032 64KB FLASH 80TQFP

Manufacturer

STMicroelectronics

Series

µPSDr

Datasheet

1.UPSD3422EV-40U6.pdf

(300 pages)

Specifications of UPSD3422E-40U6

Core Processor

8032

Core Size

8-Bit

Speed

40MHz

Connectivity

I²C, IrDA, SPI, UART/USART, USB

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

46

Program Memory Size

80KB (80K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-TQFP, 80-VQFP

For Use With

497-5577 - BOARD EVAL USB POWER SWITCH497-5518 - EVAL BOARD RFID READER

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Other names

497-4903

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

UPSD3422E-40U6

Manufacturer:

STMicroelectronics

Quantity:

10 000

- Current page: 256 of 300

- Download datasheet (3Mb)

PSD module

Table 203. Function status during power-up reset, warm reset, power-down mode

256/300

Output of OMC Flip-flops

Port configuration or

PMMR0 and PMMR2

JTAG ISP and debug

Latched address out

Peripheral I/O mode

MCU I/O

register

PLD I/O

mode

Upon power-up, and while RST is asserted, the PSD module immediately loads its

configuration from non-volatile bits to configure the PLDs and other items. PLD logic is

operational and ready for use well before RST is de-asserted. The state of PLD outputs are

determined by equations specified in PSDsoft Express.

The Flash memories are reset to Read Array mode after any assertion of RST (even if a

program or erase operation is occurring).

Flash memory WRITE operations are automatically prevented while V

it rises above the V

are allowed.

Once the UPSD34xx is up and running, any subsequent reset operation is referred to as a

warm reset, until power is turned off again. Some PSD module functions are reset in

different ways depending if the reset condition was caused from a power-up reset or a warm

reset.

power-up and warm resets, as well as the affect of PSD module power-down mode (from

APD).

The I/O pins of PSD module Ports A, B, C, and D do not have weak internal pull-ups.

In MCU I/O mode, Latched Address Out mode, and Peripheral I/O mode, the pins of Ports

A, B, C, and D become standard CMOS inputs during a reset condition. If no external

devices are driving these pins during reset, then these inputs may float and draw excessive

current. If low power consumption is critical during reset, then these floating inputs should

be pulled up externally to V

In PLD I/O mode, pins of Ports A, B, C, and D may also float during reset if no external

device is driving them, and if there is no equation specified for the DPLD or GPLD to make

them an output. In this case, a weak external pull-up resistor (100KΩ minimum) should be

used on floating pins to avoid excessive current draw.

The pins on Ports 1, 3, and 4 of the 8032 MCU module do have weak internal pull-ups and

the inputs will not float, so no external pull-ups are needed.

Table 203 on page 256

before RST is de-asserted

Pins are High Impedance

Pins are High Impedance

JTAG channel is active

Pins are in input mode

loaded. Happens long

Pin logic is valid after

internal PSD module

configuration bits are

Power-up reset

Cleared to 00h

Cleared to ’0’

and available

LKO

voltage threshold at which time Flash memory WRITE operations

DD

summarizes how PSD module functions are affected by

with a weak (100KΩ minimum) resistor.

Pins are High Impedance

Pins are high impedance

determined by PLD logic

Depends on .re and .pr

Pins are in input mode

Pin logic is valid and is

JTAG channel is active

UPSD3422, UPSD3433, UPSD3434, UPSD3454

and available

Warm reset

Unchanged

equations

equations

Pin logic depends on inputs to

Pin logic state is unchanged

since 8032 address signals

blocked from reaching PLD

Pins logic state not defined

JTAG channel is active and

PLD (8032 addresses are

inputs during power-down

Pins are High Impedance

APD Power-down mode

Depends on .re and .pr

DD

are blocked

Unchanged

equations

is ramping up until

available

mode)

Related parts for UPSD3422E-40U6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Fast Turbo 8032 MCU with USB and Programmable Logic

Manufacturer:

STMICROELECTRONICS [STMicroelectronics]

Datasheet:

Part Number:

Description:

MCU 8BIT 8032 64KB FLASH 52TQFP

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet: