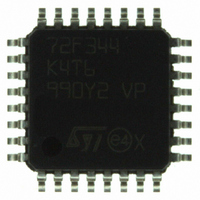

ST72F344K4T6 STMicroelectronics, ST72F344K4T6 Datasheet - Page 142

ST72F344K4T6

Manufacturer Part Number

ST72F344K4T6

Description

MCU 8BIT 16KB FLASH MEM 32-LQFP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST72F344K2T6.pdf

(247 pages)

Specifications of ST72F344K4T6

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, LIN, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

24

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

Processor Series

ST72F3x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

I2C, SCI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

34

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

ST72F34X-SK/RAIS, ST7MDT40-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

497-5046 - KIT TOOL FOR ST7/UPSD/STR7 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-5611

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST72F344K4T6

Manufacturer:

STMicroelectronics

Quantity:

10 000

Company:

Part Number:

ST72F344K4T6TR

Manufacturer:

STMicroelectronics

Quantity:

10 000

- Current page: 142 of 247

- Download datasheet (3Mb)

On-chip peripherals

11.5.6

11.5.7

Note:

Note:

142/247

Interrupts

Table 58.

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control Bit is set and the

interrupt mask in the CC register is reset (RIM instruction).

Register description

Status register (SCISR)

Reset value: 1100 0000 (C0h)

Bit 7 = TDRE Transmit data register empty.

Data is not transferred to the shift register until the TDRE bit is cleared.

Bit 6 = TC Transmission complete.

TC is not set after the transmission of a Preamble or a Break.

Bit 5 = RDRF Received data ready flag.

Transmit data register empty

Transmission complete

Received data ready to be read

Overrun error detected

Idle line detected

Parity error

TDRE

This bit is set by hardware when the content of the TDR register has been transferred

into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register.

It is cleared by a software sequence (an access to the SCISR register followed by a

write to the SCIDR register).

0: Data is not transferred to the shift register

1: Data is transferred to the shift register

This bit is set by hardware when transmission of a frame containing Data is complete.

An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software

sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

This bit is set by hardware when the content of the RDR register has been transferred

to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2 register. It is

7

Interrupt event

Interrupt events

TC

RDRF

Doc ID 12321 Rev 5

TDRE

TC

RDRF

OR

IDLE

PE

Event flag

IDLE

Read-only

OR

TIE

TCIE

RIE

ILIE

PIE

Enable control

bit

NF

Yes

ST72344xx ST72345xx

Exit from

Wait

FE

No

Exit from

Halt

PE

0

Related parts for ST72F344K4T6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN Transistor Power Module

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet: