ST72F344K4T6 STMicroelectronics, ST72F344K4T6 Datasheet - Page 165

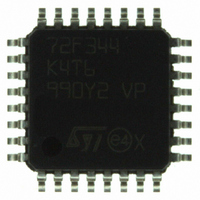

ST72F344K4T6

Manufacturer Part Number

ST72F344K4T6

Description

MCU 8BIT 16KB FLASH MEM 32-LQFP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST72F344K2T6.pdf

(247 pages)

Specifications of ST72F344K4T6

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, LIN, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

24

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

Processor Series

ST72F3x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

I2C, SCI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

34

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

ST72F34X-SK/RAIS, ST7MDT40-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

497-5046 - KIT TOOL FOR ST7/UPSD/STR7 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-5611

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST72F344K4T6

Manufacturer:

STMicroelectronics

Quantity:

10 000

Company:

Part Number:

ST72F344K4T6TR

Manufacturer:

STMicroelectronics

Quantity:

10 000

- Current page: 165 of 247

- Download datasheet (3Mb)

ST72344xx ST72345xx

Note:

I

Reset value: 0000 0000 (00h)

Bits 7:0 = D[7:0] 8-bit Data Register.

●

●

I

Reset value: 0000 0000 (00h)

7-bit addressing mode

Bits 7:1 = ADD[7:1] Interface address.

Bit 0 = ADD0 Address direction bit.

Address 01h is always ignored.

10-bit addressing mode

Bit 7:0 = ADD[7:0] Interface address.

2

2

C data register (DR)

C own address register (OAR1)

ADD7

D7

These bits contain the byte to be received or transmitted on the bus.

Transmitter mode: byte transmission start automatically when the software writes in the

DR register.

Receiver mode: the first data byte is received automatically in the DR register using the

least significant bit of the address.

Then, the following data bytes are received one by one after reading the DR register.

These bits define the I

interface is disabled (PE=0).

This bit is don’t care, the interface acknowledges either 0 or 1. It is not cleared when

the interface is disabled (PE=0).

These are the least significant bits of the I

cleared when the interface is disabled (PE=0).

7

7

ADD6

D6

ADD5

2

D5

C bus address of the interface. They are not cleared when the

Doc ID 12321 Rev 5

ADD4

D4

Read / Write

Read / Write

2

C bus address of the interface. They are not

ADD3

D3

ADD2

D2

On-chip peripherals

ADD1

D1

ADD0

165/247

D0

0

0

Related parts for ST72F344K4T6

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

STMicroelectronics [RIPPLE-CARRY BINARY COUNTER/DIVIDERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

STMicroelectronics [LIQUID-CRYSTAL DISPLAY DRIVERS]

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

BOARD EVAL FOR MEMS SENSORS

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN TRANSISTOR POWER MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

TURBOSWITCH ULTRA-FAST HIGH VOLTAGE DIODE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search -----> STE16N100

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

Search ---> STE53NA50

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

NPN Transistor Power Module

Manufacturer:

STMicroelectronics

Datasheet:

Part Number:

Description:

DIODE / SCR MODULE

Manufacturer:

STMicroelectronics

Datasheet: