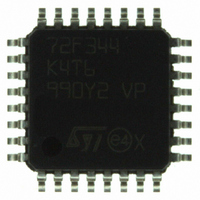

ST72F344K4T6 STMicroelectronics, ST72F344K4T6 Datasheet - Page 239

ST72F344K4T6

Manufacturer Part Number

ST72F344K4T6

Description

MCU 8BIT 16KB FLASH MEM 32-LQFP

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST72F344K2T6.pdf

(247 pages)

Specifications of ST72F344K4T6

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, LIN, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

24

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

1K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

Processor Series

ST72F3x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

1 KB

Interface Type

I2C, SCI, SPI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

34

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

ST72F34X-SK/RAIS, ST7MDT40-EMU3, STX-RLINK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

For Use With

497-5046 - KIT TOOL FOR ST7/UPSD/STR7 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-5611

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST72F344K4T6

Manufacturer:

STMicroelectronics

Quantity:

10 000

Company:

Part Number:

ST72F344K4T6TR

Manufacturer:

STMicroelectronics

Quantity:

10 000

ST72344xx ST72345xx

16

16.1

16.1.1

Known limitations

External interrupt missed

To avoid any risk if generating a parasitic interrupt, the edge detector is automatically

disabled for one clock cycle during an access to either DDR and OR. Any input signal edge

during this period will not be detected and will not generate an interrupt.

This case can typically occur if the application refreshes the port configuration registers at

intervals during runtime.

Workaround

The workaround is based on software checking the level on the interrupt pin before and after

writing to the PxOR or PxDDR registers. If there is a level change (depending on the

sensitivity programmed for this pin) the interrupt routine is invoked using the call instruction

with three extra PUSH instructions before executing the interrupt routine (this is to make the

call compatible with the IRET instruction at the end of the interrupt service routine).

But detection of the level change does not make sure that edge occurs during the critical 1

cycle duration and the interrupt has been missed. This may lead to occurrence of same

interrupt twice (one hardware and another with software call).

To avoid this, a semaphore is set to '1' before checking the level change. The semaphore is

changed to level '0' inside the interrupt routine. When a level change is detected, the

semaphore status is checked and if it is '1' this means that the last interrupt has been

missed. In this case, the interrupt routine is invoked with the call instruction.

There is another possible case i.e. if writing to PxOR or PxDDR is done with global

interrupts disabled (interrupt mask bit set). In this case, the semaphore is changed to '1'

when the level change is detected. Detecting a missed interrupt is done after the global

interrupts are enabled (interrupt mask bit reset) and by checking the status of the

semaphore. If it is '1' this means that the last interrupt was missed and the interrupt routine

is invoked with the call instruction.

To implement the workaround, the following software sequence is to be followed for writing

into the PxOR/PxDDR registers. The example is for Port PF1 with falling edge interrupt

sensitivity. The software sequence is given for both cases (global interrupt

disabled/enabled).

Case 1: Writing to PxOR or PxDDR with global interrupts enabled:

LD A,#01

LD sema,A; set the semaphore to '1'

LD A,PFDR

AND A,#02

LD

LD A,#$90

LD PFDDR,A; Write to PFDDR

LD A,#$ff

LD

X,A; store the level before writing to PxOR/PxDDR

PFOR,A; Write to PFOR

Doc ID 12321 Rev 5

Known limitations

239/247