EVAL-ADAU1761Z Analog Devices Inc, EVAL-ADAU1761Z Datasheet - Page 48

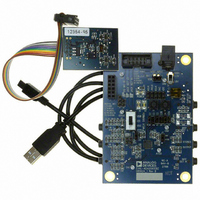

EVAL-ADAU1761Z

Manufacturer Part Number

EVAL-ADAU1761Z

Description

Eval Board For ADAU1761

Manufacturer

Analog Devices Inc

Series

SigmaDSP®r

Specifications of EVAL-ADAU1761Z

Main Purpose

Audio, CODEC

Embedded

Yes, DSP

Utilized Ic / Part

ADAU1761

Primary Attributes

Stereo, 24-Bit, 8 ~ 96 kHz Sampling Rate, GUI Tool

Secondary Attributes

I²C and GPIO Interfaces, 2 Differential and 1 Stereo Single-Ended Analog Inputs and Outputs

Silicon Manufacturer

Analog Devices

Core Architecture

SigmaDSP

Silicon Core Number

ADAU1761

Silicon Family Name

SigmaDSP

Application Sub Type

Audio

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EVAL-ADAU1761Z

Manufacturer:

Analog Devices Inc

Quantity:

135

ADAU1761

Table 27. Parameter RAM Read/Write Format (Single Address)

Byte 0

chip_adr[6:0], R/W

Table 28. Parameter RAM Block Read/Write Format (Burst Mode)

Byte 0

chip_adr[6:0], R/W

Table 29. Program RAM Read/Write Format (Single Address)

Byte 0

chip_adr[6:0], R/W

Table 30. Program RAM Block Read/Write Format (Burst Mode)

Byte 0

chip_adr[6:0], R/W

SOFTWARE SAFELOAD

To update parameters in real time while avoiding pop and click

noises on the output, the ADAU1761 uses a software safeload

mechanism. The software safeload mechanism enables the

SigmaDSP core to load new parameters into RAM while guar-

anteeing that the parameters are not in use. This prevents an

undesirable condition where an instruction could execute with

a mix of old and new parameters.

SigmaStudio sets up the necessary code and parameters auto-

matically for new projects. The safeload code, along with other

initialization code, fills the first 39 locations in program RAM.

The first eight parameter RAM locations (Address 0x0000 to

Address 0x0007) are configured by default in SigmaStudio as

described in Table 31.

Table 31. Software Safeload Parameter RAM Defaults

Address (Hex)

0x0000

0x0001

0x0002

0x0003

0x0004

0x0005

0x0006

0x0007

Address 0x0000, which controls the modulo RAM size, is set

by SigmaStudio and is based on the dynamic address generator

mode of the project.

Function

Modulo RAM size

Safeload Data 1

Safeload Data 2

Safeload Data 3

Safeload Data 4

Safeload Data 5

Safeload target address (offset of −1)

Number of words to write/safeload trigger

Byte 1

param_adr[15:8]

Byte 1

prog_adr[15:8]

Byte 1

param_adr[15:8]

Byte 1

prog_adr[15:8]

Byte 2

prog_adr[7:0]

Byte 2

param_adr[7:0]

Byte 2

param_adr[7:0]

Byte 2

prog_adr[7:0]

Rev. C | Page 48 of 92

Byte 3

0000, param[27:24]

Bytes[3:7]

prog[39:0]

<—prog_adr—>

<—param_adr—>

Parameter RAM Address 0x0001 to Address 0x0005 are the five

data slots for storing the data to be safeloaded. The safeload

parameter space contains five data slots by default because most

standard signal processing algorithms have five parameters or less.

Address 0x0006 is the target address in parameter RAM (with

an offset of −1). This designates the first address to be written.

If more than one word is written, the address increments auto-

matically for each data-word. Up to five sequential parameter

RAM locations can be updated with safeload during each audio

frame. The target address offset of −1 is used because the write

address is calculated relative to the address of the data, which

starts at Address 0x0001. Therefore, to update a parameter at

Address 0x000A, the target address is 0x0009.

Address 0x0007 designates the number of words to be written

into the parameter RAM during the safeload. A biquad filter

uses all five safeload data addresses. A simple mono gain cell

uses only one safeload data address. Writing to Address 0x0007

also triggers the safeload write to occur in the next audio frame.

The safeload mechanism is software based and executes once

per audio frame. Therefore, system designers must take care

when designing the communication protocol. A delay equal to

or greater than the sampling period (the inverse of sampling

frequency) is required between each safeload write. A sample

rate of 48 kHz equates to a delay of at least 21 μs. If this delay

is not observed, the downloaded data is corrupted.

Byte 3

0000, param[27:24]

Bytes[3:7]

prog[39:0]

Bytes[4:6]

param[23:0]

Bytes[8:12]

prog_adr + 1

Bytes[7:10]

param_adr + 1

param[23:0]

Bytes[4:6]

Bytes[13:17]

prog_adr + 2

Bytes[11:14]

param_adr + 2