EVAL-ADAU1761Z Analog Devices Inc, EVAL-ADAU1761Z Datasheet - Page 82

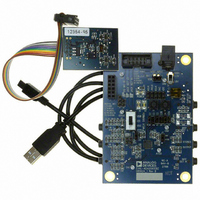

EVAL-ADAU1761Z

Manufacturer Part Number

EVAL-ADAU1761Z

Description

Eval Board For ADAU1761

Manufacturer

Analog Devices Inc

Series

SigmaDSP®r

Specifications of EVAL-ADAU1761Z

Main Purpose

Audio, CODEC

Embedded

Yes, DSP

Utilized Ic / Part

ADAU1761

Primary Attributes

Stereo, 24-Bit, 8 ~ 96 kHz Sampling Rate, GUI Tool

Secondary Attributes

I²C and GPIO Interfaces, 2 Differential and 1 Stereo Single-Ended Analog Inputs and Outputs

Silicon Manufacturer

Analog Devices

Core Architecture

SigmaDSP

Silicon Core Number

ADAU1761

Silicon Family Name

SigmaDSP

Application Sub Type

Audio

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EVAL-ADAU1761Z

Manufacturer:

Analog Devices Inc

Quantity:

135

ADAU1761

R52 to R56: Watchdog Registers, 16,592 to 16,596 (0x40D0 to 0x40D4)

A program counter watchdog is used when the core does block processing (which can span several samples). The watchdog flags an error

if the program counter reaches a specific 24-bit value (ranging from 0x000000 to 0xFFFFFF) that is set in the register map. This value

consists of three consecutive 8-bit register locations. The error flag sends a high signal to one of the GPIO pins. The watchdog function

must be enabled by setting the DOGEN bit high in Register R52 (Address 0x40D0).

The watchdog error bit (DOGER) is the 1-bit watchdog error flag that can be sent to a GPIO pin, as described in Table 79. This error flag

can connect, for example, to an interrupt pin on a microcontroller in the system. The flag is reset when the DOGEN bit goes low. This

flag can also be read back over the control port from Register R56 (Address 0x40D4).

Address

0x40D0

0x40D1

0x40D2

0x40D3

0x40D4

Table 81. Watchdog Registers

Register

R52

R53

R54

R55

R56

R57: DSP Sampling Rate Setting, 16,619 (0x40EB)

Bit 7

Table 82. DSP Sampling Rate Setting Register

Bits

[3:0]

Bit Name

DSPSR[3:0]

Bit 7

Decimal

16,592

16,593

16,594

16,595

16,596

Bit 6

Address

Description

SigmaDSP core sampling rate. The DSP sampling rate is a ratio of the base sampling rate, f

is determined by the operating frequency of the core clock. For most applications, the SigmaDSP core sampling

rate should equal the converter sampling rate (set using the CONVSR[2:0] bits in Register R17) and the serial

port sampling rate (set using the SPSR[2:0] bits in Register R64).

Setting

0000

0001

0010

0011

0100

0101

0110

0111

1000

1111

Reserved

Hex

0x40D0

0x40D1

0x40D2

0x40D3

0x40D4

Bit 6

Bit 5

Bit Name

DOGEN

DOG[23:16]

DOG[15:8]

DOG[7:0]

DOGER

Bit 5

Bit 4

Description

Watchdog enable bit.

0 = disabled (default).

1 = enabled.

Watchdog value, Bits[23:16] (MSB).

Watchdog value, Bits[15:8].

Watchdog value, Bits[7:0].

DOG[23:16]

00000000

…

11111111

Watchdog error (read-only bit).

0 = no error (default).

1 = error.

Sampling Rate

f

f

f

f

f

f

f

Serial input data rate

Serial output data rate

None

S

S

S

S

S

S

S

Rev. C | Page 82 of 92

/0.5

/1.5

/2

/3

/4

/6

Bit 4

Reserved

Reserved

Bit 3

DOG[23:16]

DOG[15:8]

DOG[7:0]

Bit 3

DOG[15:8]

00000000

…

11111111

Bit 2

Base Sampling Rate (f

96 kHz, base

48 kHz (default)

32 kHz

24 kHz

16 kHz

12 kHz

8 kHz

Bit 2

DOG[7:0]

00000000

…

11111111

DSPSR[3:0]

Bit 1

Bit 1

S

S

. The base sampling rate

= 48 kHz)

Hex Value

0x000000 (default)

…

0xFFFFFF

Bit 0

Bit 0

DOGEN

DOGER