EVAL-ADAU1761Z Analog Devices Inc, EVAL-ADAU1761Z Datasheet - Page 66

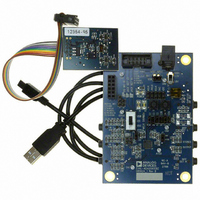

EVAL-ADAU1761Z

Manufacturer Part Number

EVAL-ADAU1761Z

Description

Eval Board For ADAU1761

Manufacturer

Analog Devices Inc

Series

SigmaDSP®r

Specifications of EVAL-ADAU1761Z

Main Purpose

Audio, CODEC

Embedded

Yes, DSP

Utilized Ic / Part

ADAU1761

Primary Attributes

Stereo, 24-Bit, 8 ~ 96 kHz Sampling Rate, GUI Tool

Secondary Attributes

I²C and GPIO Interfaces, 2 Differential and 1 Stereo Single-Ended Analog Inputs and Outputs

Silicon Manufacturer

Analog Devices

Core Architecture

SigmaDSP

Silicon Core Number

ADAU1761

Silicon Family Name

SigmaDSP

Application Sub Type

Audio

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EVAL-ADAU1761Z

Manufacturer:

Analog Devices Inc

Quantity:

135

ADAU1761

R19: ADC Control, 16,409 (0x4019)

Bit 7

Reserved

Table 53. ADC Control Register

Bits

6

5

4

3

2

[1:0]

R20: Left Input Digital Volume, 16,410 (0x401A)

Bit 7

Table 54. Left Input Digital Volume Register

Bits

[7:0]

Bit Name

ADCPOL

HPF

DMPOL

DMSW

INSEL

ADCEN[1:0]

Bit Name

LADVOL[7:0]

Bit 6

ADCPOL

Bit 6

Description

Invert input polarity.

0 = normal (default).

1 = inverted.

ADC high-pass filter select. At 48 kHz, f

0 = off (default).

1 = on.

Digital microphone data polarity swap.

0 = invert polarity.

1 = normal (default).

Digital microphone channel swap. Normal operation sends the left channel on the rising edge of the clock and

the right channel on the falling edge of the clock.

0 = normal (default).

1 = swap left and right channels.

Digital microphone input select. When asserted, the on-chip ADCs are off, BCLK is master at 128 × f

ADC_SDATA is expected to have left and right channels interleaved.

0 = digital microphone inputs off, ADCs enabled (default).

1 = digital microphone inputs enabled, ADCs off.

ADC enable.

Setting

00

01

10

11

Description

Controls the digital volume attenuation for left channel inputs from either the left ADC or the left digital

microphone input. Each bit corresponds to a 0.375 dB step with slewing between settings. See Table 94 for a

complete list of the volume settings.

Setting

00000000

00000001

00000010

…

11111110

11111111

Bit 5

HPF

Bit 5

Bit 4

DMPOL

Bit 4

ADCs Enabled

Both off (default)

Left on

Right on

Both on

Volume Attenuation

0 dB (default)

−0.375 dB

−0.75 dB

…

−95.25 dB

−95.625 dB

Rev. C | Page 66 of 92

LADVOL[7:0]

3dB

= 2 Hz.

Bit 3

DMSW

Bit 3

Bit 2

INSEL

Bit 2

Bit 1

Bit 1

ADCEN[1:0]

Bit 0

Bit 0

S

, and