EVAL-ADAU1761Z Analog Devices Inc, EVAL-ADAU1761Z Datasheet - Page 85

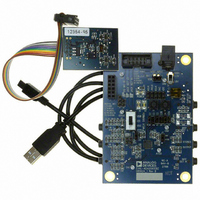

EVAL-ADAU1761Z

Manufacturer Part Number

EVAL-ADAU1761Z

Description

Eval Board For ADAU1761

Manufacturer

Analog Devices Inc

Series

SigmaDSP®r

Specifications of EVAL-ADAU1761Z

Main Purpose

Audio, CODEC

Embedded

Yes, DSP

Utilized Ic / Part

ADAU1761

Primary Attributes

Stereo, 24-Bit, 8 ~ 96 kHz Sampling Rate, GUI Tool

Secondary Attributes

I²C and GPIO Interfaces, 2 Differential and 1 Stereo Single-Ended Analog Inputs and Outputs

Silicon Manufacturer

Analog Devices

Core Architecture

SigmaDSP

Silicon Core Number

ADAU1761

Silicon Family Name

SigmaDSP

Application Sub Type

Audio

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EVAL-ADAU1761Z

Manufacturer:

Analog Devices Inc

Quantity:

135

R63: DSP Slew Modes, 16,631 (0x40F7)

The DSP slew modes register sets the slew source for each output. The slew source can be either the DSP (digital slew) or the codec (analog

slew). When these bits are set to Logic 0, the codec provides volume slew according to the ASLEW[1:0] bits in Register R34 (playback

pop/click suppression register, Address 0x4028). When these bits are set to Logic 1, the slew is provided and defined by the DSP program,

disabling the codec volume slew.

Bit 7

Table 88. DSP Slew Modes Register

Bits

4

3

2

1

0

R64: Serial Port Sampling Rate, 16,632 (0x40F8)

Bit 7

Table 89. Serial Port Sampling Rate Register

Bits

[2:0]

Bit Name

MOSLW

ROSLW

LOSLW

RHPSLW

LHPSLW

Bit Name

SPSR[2:0]

Bit 6

Bit 6

Reserved

Headphone right slew generation.

Headphone left slew generation.

Description

Mono output slew generation.

0 = codec (default).

1 = DSP.

Line output right slew generation.

0 = codec (default).

1 = DSP.

Line output left slew generation.

0 = codec (default).

1 = DSP.

0 = codec (default).

1 = DSP.

0 = codec (default).

1 = DSP.

Description

Serial port sampling rate. The serial port sampling rate is a ratio of the base sampling rate, f

rate is determined by the operating frequency of the core clock. For most applications, the serial port sampling

rate should equal the converter sampling rate (set using the CONVSR[2:0] bits in Register R17) and the DSP sampling

rate (set using the DSPSR[3:0] bits in Register R57).

Setting

000

001

010

011

100

101

110

111

Bit 5

Bit 5

Reserved

Bit 4

MOSLW

Bit 4

Sampling Rate

f

f

f

f

f

f

f

Reserved

S

S

S

S

S

S

S

Rev. C | Page 85 of 92

/6

/4

/3

/2

/1.5

/0.5

Bit 3

ROSLW

Bit 3

Bit 2

LOSLW

Bit 2

Base Sampling Rate (f

48 kHz, base (default)

8 kHz

12 kHz

16 kHz

24 kHz

32 kHz

96 kHz

Bit 1

RHPSLW

Bit 1

SPSR[2:0]

S

= 48 kHz)

S

. The base sampling

ADAU1761

Bit 0

LHPSLW

Bit 0