EP1S80B956C7N Altera, EP1S80B956C7N Datasheet - Page 434

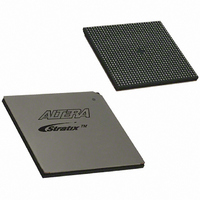

EP1S80B956C7N

Manufacturer Part Number

EP1S80B956C7N

Description

IC STRATIX FPGA 80K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S80B956C7N

Number Of Logic Elements/cells

79040

Number Of Labs/clbs

7904

Total Ram Bits

7427520

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 434 of 864

- Download datasheet (11Mb)

Stratix & Stratix GX I/O Standards

4–6

Stratix Device Handbook, Volume 2

1.5-V Differential HSTL - EIA/JEDEC Standard EIA/JESD8-6

The differential HSTL I/O standard is used for applications designed to

operate in the 0.0- to 1.5-V HSTL logic switching range such as quad data

rate (QDR) memory clock interfaces. The differential HSTL specification

is the same as the single ended HSTL specification. The standard specifies

an input voltage range of – 0.3 V V

does not require an input reference voltage, however, it does require a

50

Figure

clock levels for 1.5-V differential HSTL. The input clock is implemented

using dedicated differential input buffer. Two single-ended output

buffers are automatically programmed to have opposite polarity so as to

implement a differential output clock.

Figure 4–3. 1.5-V Differential HSTL Class I Termination

3.3-V PCI Local Bus - PCI Special Interest Group PCI Local Bus

Specification Rev. 2.3

The PCI local bus specification is used for applications that interface to

the PCI local bus, which provides a processor-independent data path

between highly integrated peripheral controller components, peripheral

add-in boards, and processor/memory systems. The conventional PCI

specification revision 2.3 defines the PCI hardware environment

including the protocol, electrical, mechanical, and configuration

specifications for the PCI devices and expansion boards. This standard

requires 3.3-V V

with the 3.3-V PCI Local Bus Specification Revision 2.3 and meet

64-bit/66-MHz operating frequency and timing requirements. The 3.3-V

PCI standard does not require input reference voltages or board

terminations. Stratix and Stratix GX devices support both input and

output levels.

Transmitter

resistor termination resistor to V

Differential

4–3). Stratix and Stratix GX devices support both input and output

CCIO

. Stratix and Stratix GX devices are fully compliant

Z

Z

0

0

= 50 Ω

= 50 Ω

50 Ω

V

TT

I

= 0.75 V

TT

V

CCIO

at the input buffer (see

+ 0.3 V. Differential HSTL

50 Ω

V

TT

= 0.75 V

Altera Corporation

Differential

Receiver

June 2006

Related parts for EP1S80B956C7N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: