EP1S80B956C7N Altera, EP1S80B956C7N Datasheet - Page 455

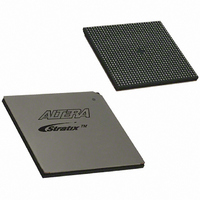

EP1S80B956C7N

Manufacturer Part Number

EP1S80B956C7N

Description

IC STRATIX FPGA 80K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S80B956C7N

Number Of Logic Elements/cells

79040

Number Of Labs/clbs

7904

Total Ram Bits

7427520

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 455 of 864

- Download datasheet (11Mb)

Hot Socketing

Altera Corporation

June 2006

Programmable Current Drive Strength

The Stratix and Stratix GX device I/O pins support various output

current drive settings as shown in

strength settings help decrease the effects of simultaneously switching

outputs (SSO) in conjunction with reducing system noise. The supported

settings ensure that the device driver meets the I

for the corresponding I/O standard.

These drive-strength settings are programmable on a per-pin basis (for

output and bidirectional pins only) using the Quartus II software. To

modify the current strength of a particular pin, see

Strength Settings” on page

Stratix devices support hot socketing without any external components.

In a hot socketing situation, a device’s output buffers are turned off

during system power-up or power-down. Stratix and Stratix GX devices

support any power-up or power-down sequence (V

simplify designs. For mixed-voltage environments, you can drive signals

into the device before or during power-up or power-down without

damaging the device. Stratix and Stratix GX devices do not drive out until

the device is configured and has attained proper operating conditions.

Even though you can power up or down the V

supplies in any sequence you should not power down any I/O bank(s)

that contains the configuration pins while leaving other I/O banks

powered on. For power up and power down, all supplies (V

V

another. This prevents I/O pins from driving out.

Notes to

(1)

(2)

3.3-V LVTTL

3.3-V LVCMOS

2.5-V LVTTL/LVCMOS

1.8-V LVTTL/LVCMOS

1.5-V LVCMOS

Table 4–7. Programmable Drive Strength

CCIO

This is the Quartus II software default current setting.

I/O banks 1, 2, 5, and 6 do not support this setting.

power planes) must be powered up and down within 100 ms of one

I/O Standard

Table

4–7:

Selectable I/O Standards in Stratix & Stratix GX Devices

4–40.

24 (1), 16, 12, 8, 4

24 (2), 12 (1), 8, 4, 2

16 (1), 12, 8, 2

12 (1), 8, 2

8 (1), 4, 2

I

OH

Table

/ I

OL

Stratix Device Handbook, Volume 2

Current Strength Setting (mA)

4–7. These programmable drive

CCIO

OH

“Programmable Drive

and I

and V

CCIO

OL

and V

CCINT

specifications

CCINT

CCINT

power

and all

) to

4–27

Related parts for EP1S80B956C7N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: