EP1S80B956C7N Altera, EP1S80B956C7N Datasheet - Page 713

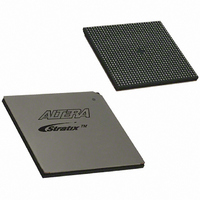

EP1S80B956C7N

Manufacturer Part Number

EP1S80B956C7N

Description

IC STRATIX FPGA 80K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S80B956C7N

Number Of Logic Elements/cells

79040

Number Of Labs/clbs

7904

Total Ram Bits

7427520

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 713 of 864

- Download datasheet (11Mb)

Altera Corporation

July 2005

input_data_rate

inclock_data_alignment

rx_data_align

registered_data_align_input

common_rx_tx_pll

output_data_rate

inclock_data_alignment

outclock_alignment

Table 10–11. New altlvds Parameters for Stratix LVDS Receiver

Table 10–12. New altlvds Parameters for Stratix LVDS Transmitter (Part 1 of 2)

Parameter

Parameter

f

(2)

(3)

(2)

channel as an output clock to an I/O pin, not just dedicated clock output

pins. This solution offers better versatility to address various applications

that require more complex clocking schemes.

For more information on differential I/O support, data realignment, and

the transmitter clock output in Stratix and Stratix GX devices, see the

High-Speed Differential I/O Interfaces in Stratix Devices chapter.

altlvds Megafunction

To take full advantage of the high-speed differential I/O standards

available in Stratix and Stratix GX devices, you should update each

instance of the altlvds megafunction in APEX II, APEX 20KE, and

APEX 20KC designs. In the MegaWizard Plug-In Manager, choose the

altlvds megafunction, select Stratix or Stratix GX as the target device

family, update the megafunction, and recompile your design.

The altlvds megafunction supports new Stratix and Stratix GX

parameters that are not available for APEX II, APEX 20KE, and

APEX 20KC devices.

parameters for the LVDS receiver and LVDS transmitter, respectively.

Specifies the data rate in Mbps. This parameter replaces the

multiplication factor W.

Indicates the alignment of

Drives the data alignment port of the fast PLL and enables byte

realignment circuitry.

Registers the

rx_outclock

Indicates the fast PLL can be shared between receiver and transmitter

applications.

Specifies the data rate in Mbps. This parameter replaces the

multiplication factor W.

Indicates the alignment of

Specifies the alignment of

Transitioning APEX Designs to Stratix & Stratix GX Devices

Tables 10–11

rx_data_align

.

Note (1)

rx_inclk

tx_inclk

tx_outclock

and

Function

Function

10–12

Stratix Device Handbook, Volume 2

input port to be clocked by

and

and

describe the new

Note (1)

rx_in

tx_in

and

tx_out

data.

data.

data.

10–29

Related parts for EP1S80B956C7N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: