EP1S80B956C7N Altera, EP1S80B956C7N Datasheet - Page 456

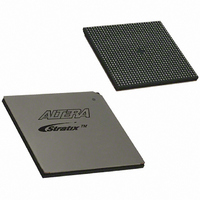

EP1S80B956C7N

Manufacturer Part Number

EP1S80B956C7N

Description

IC STRATIX FPGA 80K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S80B956C7N

Number Of Logic Elements/cells

79040

Number Of Labs/clbs

7904

Total Ram Bits

7427520

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 456 of 864

- Download datasheet (11Mb)

I/O Termination

I/O Termination

4–28

Stratix Device Handbook, Volume 2

You can power up or power down the V

sequence. The power supply ramp rates can range from 100 ns to 100 ms.

During hot socketing, the I/O pin capacitance is less than 15 pF and the

clock pin capacitance is less than 20 pF.

DC Hot Socketing Specification

The hot socketing DC specification is | I

AC Hot Socketing Specification

The hot socketing AC specification is | I

This specification takes into account the pin capacitance, but not board

trace and external loading capacitance. Additional capacitance for trace,

connector, and loading must be considered separately.

I

specification applies when all VCC supplies to the device are stable in the

powered-up or powered-down conditions. For the AC specification, the

peak current duration because of power-up transients is 10 ns or less. For

more information, refer to the Hot-Socketing & Power-Sequencing Feature &

Testing for Altera Devices white paper.

Although single-ended, non-voltage-referenced I/O standards do not

require termination, Altera recommends using external termination to

improve signal integrity where required.

The following I/O standards do not require termination:

■

■

■

■

■

■

■

■

Voltage-Referenced I/O Standards

Voltage-referenced I/O standards require both an input reference

voltage, V

board should be used for series and parallel termination.

IOPIN

LVTTL

LVCMOS

2.5 V

1.8 V

1.5 V

3.3-V PCI/Compact PCI

3.3-V PCI-X 1.0

3.3-V AGP 1

is the current at any user I/O pin on the device. The DC

REF,

and a termination voltage, V

CCIO

IOPIN

IOPIN

TT

. Off-chip termination on the

and V

| < 300 A.

| < 8 mA for 10 ns or less.

CCINT

Altera Corporation

pins in any

June 2006

Related parts for EP1S80B956C7N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: