MC9S12C64CFUE Freescale Semiconductor, MC9S12C64CFUE Datasheet - Page 212

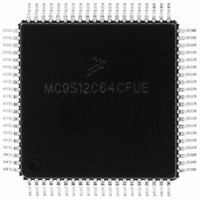

MC9S12C64CFUE

Manufacturer Part Number

MC9S12C64CFUE

Description

IC MCU 64K FLASH 4K RAM 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Specifications of MC9S12C64CFUE

Core Processor

HCS12

Core Size

16-Bit

Speed

25MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

60

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Processor Series

S12C

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

4 KB

Interface Type

CAN/SCI/SPI

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

60

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

M68EVB912C32EE

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Package

80PQFP

Family Name

HCS12

Maximum Speed

25 MHz

Operating Supply Voltage

2.5|5 V

Height

2.4 mm

Length

14 mm

Supply Voltage (max)

2.75 V, 5.5 V

Supply Voltage (min)

2.35 V, 2.97 V

Width

14 mm

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12C64CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 212 of 690

- Download datasheet (4Mb)

Chapter 7 Debug Module (DBGV1) Block Description

7.4

This section provides a complete functional description of the DBG module. The DBG module can be

configured to run in either of two modes, BKP or DBG. BKP mode is enabled by setting BKABEN in

DBGC2. DBG mode is enabled by setting DBGEN in DBGC1. Setting BKABEN in DBGC2 overrides the

DBGEN in DBGC1 and prevents DBG mode. If the part is in secure mode, DBG mode cannot be enabled.

7.4.1

In BKP mode, the DBG will be fully backwards compatible with the existing BKP_ST12_A module. The

DBGC2 register has four additional bits that were not available on existing BKP_ST12_A modules. As

long as these bits are written to either all 1s or all 0s, they should be transparent to the user. All 1s would

enable comparator C to be used as a breakpoint, but tagging would be enabled. The match address register

would be all 0s if not modified by the user. Therefore, code executing at address 0x0000 would have to

occur before a breakpoint based on comparator C would happen.

The DBG module in BKP mode supports two modes of operation: dual address mode and full breakpoint

mode. Within each of these modes, forced or tagged breakpoint types can be used. Forced breakpoints

occur at the next instruction boundary if a match occurs and tagged breakpoints allow for breaking just

before the tagged instruction executes. The action taken upon a successful match can be to either place the

CPU in background debug mode or to initiate a software interrupt.

The breakpoint can operate in dual address mode or full breakpoint mode. Each of these modes is

discussed in the subsections below.

7.4.1.1

When dual address mode is enabled, two address breakpoints can be set. Each breakpoint can cause the

system to enter background debug mode or to initiate a software interrupt based upon the state of BDM in

212

Module Base + 0x002F

Starting address location affected by INITRG register setting.

Reset

Field

15:0

15:0

W

R

Functional Description

DBG Operating in BKP Mode

Bit 7

Comparator B Compare Bits — The comparator B compare bits control whether comparator B compares the

address bus bits [15:0] or data bus bits [15:0] to a logic 1 or logic 0. See

0 Compare corresponding address bit to a logic 0, compares to data if in Full mode

1 Compare corresponding address bit to a logic 1, compares to data if in Full mode

Dual Address Mode

0

7

Figure 7-21. Debug Comparator B Register Low (DBGCBL)

Bit 6

0

6

Table 7-23. DBGCB Field Descriptions

MC9S12C-Family / MC9S12GC-Family

Bit 5

0

5

Rev 01.24

Bit 4

0

4

Description

Bit 3

0

3

Table

Bit 2

0

2

7-20.

Freescale Semiconductor

Bit 1

0

1

Bit 0

0

0

Related parts for MC9S12C64CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: