MC9S12C64CFUE Freescale Semiconductor, MC9S12C64CFUE Datasheet - Page 456

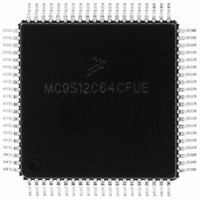

MC9S12C64CFUE

Manufacturer Part Number

MC9S12C64CFUE

Description

IC MCU 64K FLASH 4K RAM 80-QFP

Manufacturer

Freescale Semiconductor

Series

HCS12r

Specifications of MC9S12C64CFUE

Core Processor

HCS12

Core Size

16-Bit

Speed

25MHz

Connectivity

CAN, EBI/EMI, SCI, SPI

Peripherals

POR, PWM, WDT

Number Of I /o

60

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

2.35 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

80-QFP

Processor Series

S12C

Core

HCS12

Data Bus Width

16 bit

Data Ram Size

4 KB

Interface Type

CAN/SCI/SPI

Maximum Clock Frequency

25 MHz

Number Of Programmable I/os

60

Number Of Timers

8

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWHCS12

Development Tools By Supplier

M68EVB912C32EE

Minimum Operating Temperature

- 40 C

On-chip Adc

8-ch x 10-bit

Package

80PQFP

Family Name

HCS12

Maximum Speed

25 MHz

Operating Supply Voltage

2.5|5 V

Height

2.4 mm

Length

14 mm

Supply Voltage (max)

2.75 V, 5.5 V

Supply Voltage (min)

2.35 V, 2.97 V

Width

14 mm

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC9S12C64CFUE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 456 of 690

- Download datasheet (4Mb)

Chapter 15 Timer Module (TIM16B8CV1) Block Description

456

PAOVF

Field

PAIF

1

0

Pulse Accumulator Overflow Flag — Set when the 16-bit pulse accumulator overflows from 0xFFFF to 0x0000.

Clearing this bit requires wirting a one to this bit in the PAFLG register while TEN bit of TSCR1 register is set to

one.

Pulse Accumulator Input edge Flag — Set when the selected edge is detected at the IOC7 input pin.In event

mode the event edge triggers PAIF and in gated time accumulation mode the trailing edge of the gate signal at

the IOC7 input pin triggers PAIF.

Clearing this bit requires writing a one to this bit in the PAFLG register while TEN bit of TSCR1 register is set to

one. Any access to the PACNT register will clear all the flags in this register when TFFCA bit in register

TSCR(0x0006) is set.

Table 15-22. PAFLG Field Descriptions

MC9S12C-Family / MC9S12GC-Family

Rev 01.24

Description

Freescale Semiconductor

Related parts for MC9S12C64CFUE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: