SI1011-A-GM Silicon Laboratories Inc, SI1011-A-GM Datasheet - Page 124

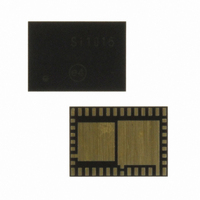

SI1011-A-GM

Manufacturer Part Number

SI1011-A-GM

Description

IC TXRX MCU + EZRADIOPRO

Manufacturer

Silicon Laboratories Inc

Specifications of SI1011-A-GM

Package / Case

42-QFN

Frequency

240MHz ~ 960MHz

Data Rate - Maximum

256kbps

Modulation Or Protocol

FSK, GFSK, OOK

Applications

General Purpose

Power - Output

20dBm

Sensitivity

-121dBm

Voltage - Supply

1.8 V ~ 3.6 V

Current - Receiving

18.5mA

Current - Transmitting

85mA

Data Interface

PCB, Surface Mount

Memory Size

8kB Flash, 768B RAM

Antenna Connector

PCB, Surface Mount

Number Of Receivers

1

Number Of Transmitters

1

Wireless Frequency

240 MHz to 960 MHz

Interface Type

UART, SMBus, SPI, PCA

Output Power

20 dBm

Operating Supply Voltage

0.9 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Maximum Supply Current

4 mA

Minimum Operating Temperature

- 40 C

Modulation

FSK, GFSK, OOK

Protocol Supported

C2, SMBus

Core

8051

Program Memory Type

Flash

Program Memory Size

8 KB

Data Ram Size

768 B

Supply Current (max)

4 mA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Operating Temperature

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1872-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SI1011-A-GM

Manufacturer:

Silicon Laboratories Inc

Quantity:

135

- Current page: 124 of 384

- Download datasheet (3Mb)

Si1010/1/2/3/4/5

9.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the

Si1010/1/2/3/4/5 devices, the MOVX instruction is normally used to read and write on-chip XRAM, but can

be re-configured to write and erase on-chip Flash memory space. MOVC instructions are always used to

read Flash memory, while MOVX write instructions are used to erase and write Flash. This Flash access

feature provides a mechanism for the Si1010/1/2/3/4/5 to update program code and use the program

memory space for non-volatile data storage. Refer to Section “13. Flash Memory” on page 146 for further

details.

9.2. Data Memory

The Si1010/1/2/3/4/5 device family include 768 bytes of RAM data memory. 256 bytes of this memory is

mapped into the internal RAM space of the 8051. The remainder of this memory is on-chip “external” mem-

ory. The data memory map is shown in Figure 9.1 for reference.

9.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The

lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either

direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00

through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight

byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or

as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the

same address space as the Special Function Registers (SFR) but is physically separate from the SFR

space. The addressing mode used by an instruction when accessing locations above 0x7F determines

whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use

direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the

upper 128 bytes of data memory. Figure 9.1 illustrates the data memory organization of the

Si1010/1/2/3/4/5.

124

(Data Only)

Scratchpad

Si1010/2/4

Si1011/3/5

(SFLE=1)

0x01FF

0x0000

Figure 9.2. Flash Program Memory Map

Flash Memory Space

Lock Byte Page

Reserved Area

Si1010/2/4

Lock Byte

(SFLE=0)

Rev. 1.0

0xFFFF

0x3C00

0x3BFF

0x3BFE

0x3A00

0x39FF

0x0000

Flash Memory Space

Lock Byte Page

Address Space

Unpopulated

Si1011/3/5

(Reserved)

(SFLE=0)

Lock Byte

0xFFFF

0x8000

0x1FFF

0x1FFE

0x1E00

0x1BFF

0x0000

Related parts for SI1011-A-GM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

QFN 42/I�/8KB, 768B RAM, +20 DBM, PROGRAMMABLE XCVR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

SMD/C�/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc