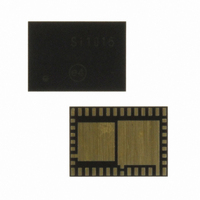

SI1011-A-GM Silicon Laboratories Inc, SI1011-A-GM Datasheet - Page 177

SI1011-A-GM

Manufacturer Part Number

SI1011-A-GM

Description

IC TXRX MCU + EZRADIOPRO

Manufacturer

Silicon Laboratories Inc

Specifications of SI1011-A-GM

Package / Case

42-QFN

Frequency

240MHz ~ 960MHz

Data Rate - Maximum

256kbps

Modulation Or Protocol

FSK, GFSK, OOK

Applications

General Purpose

Power - Output

20dBm

Sensitivity

-121dBm

Voltage - Supply

1.8 V ~ 3.6 V

Current - Receiving

18.5mA

Current - Transmitting

85mA

Data Interface

PCB, Surface Mount

Memory Size

8kB Flash, 768B RAM

Antenna Connector

PCB, Surface Mount

Number Of Receivers

1

Number Of Transmitters

1

Wireless Frequency

240 MHz to 960 MHz

Interface Type

UART, SMBus, SPI, PCA

Output Power

20 dBm

Operating Supply Voltage

0.9 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Maximum Supply Current

4 mA

Minimum Operating Temperature

- 40 C

Modulation

FSK, GFSK, OOK

Protocol Supported

C2, SMBus

Core

8051

Program Memory Type

Flash

Program Memory Size

8 KB

Data Ram Size

768 B

Supply Current (max)

4 mA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Operating Temperature

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1872-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SI1011-A-GM

Manufacturer:

Silicon Laboratories Inc

Quantity:

135

- Current page: 177 of 384

- Download datasheet (3Mb)

When the dc-dc converter “Enabled” configuration (one-cell mode) is chosen, the following guidelines

apply:

DC-DC Converter

Enabled

0.9 to 1.8 V

Supply Voltage

(one-cell mode)

DC-DC Converter

Disabled

1.8 to 3.6 V

Supply Voltage

(two-cell mode)

In most cases, the GND/VBAT– pin should not be externally connected to GND.

The 0.68 µH inductor should be placed as close as possible to the DCEN pin for maximum efficiency.

The 4.7 µF capacitor should be placed as close as possible to the inductor.

The current loop including GND/VBAT–, the 4.7 µF capacitor, the 0.68 µH inductor and the DCEN pin

should be made as short as possible to minimize capacitance.

The PCB traces connecting VDD_MCU/DC+ to the output capacitor and the output capacitor to

GND_MCU/DC– should be as short and as thick as possible in order to minimize parasitic inductance.

Figure 16.2. DC-DC Converter Configuration Options

VBAT

VBAT

Rev. 1.0

4.7 uF

GND/VBAT-

GND/VBAT-

0.68 uH

DCEN

DCEN

Si1010/1/2/3/4/5

VDD_MCU/

VDD_MCU/

DC+

DC+

GND_MCU/

GND_MCU/

DC-

DC-

1 uF

177

Related parts for SI1011-A-GM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

QFN 42/I�/8KB, 768B RAM, +20 DBM, PROGRAMMABLE XCVR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

SMD/C�/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I�/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc