R5F21238DFP#U0 Renesas Electronics America, R5F21238DFP#U0 Datasheet - Page 384

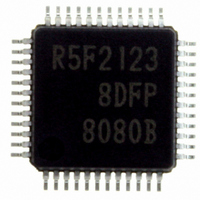

R5F21238DFP#U0

Manufacturer Part Number

R5F21238DFP#U0

Description

IC R8C/23 MCU FLASH 48-LQFP

Manufacturer

Renesas Electronics America

Series

R8C/2x/23r

Specifications of R5F21238DFP#U0

Core Size

16/32-Bit

Program Memory Size

64KB (64K x 8)

Peripherals

POR, Voltage Detect, WDT

Core Processor

R8C

Speed

20MHz

Connectivity

CAN, I²C, LIN, SIO, SSU, UART/USART

Number Of I /o

41

Program Memory Type

FLASH

Ram Size

3K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

No. Of I/o's

41

Ram Memory Size

3KB

Cpu Speed

20MHz

No. Of Timers

4

Digital Ic Case Style

LQFP

Embedded Interface Type

CAN, I2C, UART

Rohs Compliant

Yes

Cpu Family

R8C

Device Core Size

16b

Frequency (max)

20MHz

Interface Type

I2C/UART

Total Internal Ram Size

3KB

# I/os (max)

41

Number Of Timers - General Purpose

5

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

3V

On-chip Adc

12-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

48

Package Type

LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

RCDK8C - KIT DEV EVAL FOR CAN R8C/23R0K521237S000BE - KIT DEV RSK R8C/23R0E521237CPE00 - EMULATOR COMPACT R8C/20/21/22/23

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 384 of 551

- Download datasheet (6Mb)

R8C/22 Group, R8C/23 Group

Rev.2.00 Aug 20, 2008

REJ09B0251-0200

Figure 17.7

17.4.2

IR bit in the TRAIC

RXDSF flag in the

SBDCT flag in the

SFDCT flag in the

Figure 17.7 shows a Typical Operation when Receiving a Header Field. Figure 17.8 through Figure 17.10 show

an Example of Header Field Reception Flowchart.

When receiving a header field, the hardware LIN operates as described below.

LINCR register

RXD0 input for

LINST register

LINST register

(1) Synch Break detection is enabled by writing 1 to the LSTART bit in the LINCR register of the hardware

(2) When a low-level signal is input for a duration equal to or greater than the period set in timer RA, the

(3) The hardware LIN receives a Synch Field (55h). At this time, it measures the period of the start bit and

(4) The hardware LIN sets the SFDCT flag in the LINST register to 1 when it finished measuring the Synch

(5) After it finished measuring the Synch Field, the hardware LIN calculates a transfer rate from the count

(6) The hardware LIN performs communication for a response field after it finished receiving the ID field.

RXD0 pin

Slave Mode

• When LINE bit = 1 (Causes LIN to start operating), MST bit = 0 (Slave mode), SBIE bit = 1

LIN.

hardware LIN detects it as Synch Break. At this time, the SBDCT flag in the LINST register is set to 1.

Furthermore, if the SBIE bit in the LINCR register is set to 1, the hardware LIN generates a timer RA

interrupt. Then it goes to Synch Field measurement.

bits 0 to 6 by using timer RA. In this case, it is possible to select whether to input the Synch Field signal

to RxD0 of UART0 by setting the SBE bit in the LINCR register accordingly.

Field. Furthermore, if the SFIE bit in the LINCR register is set to 1, it generates a timer RA interrupt.

value of timer RA and sets the result in UART0 and sets the TRAPRE and TRA registers of the timer

RA back again. Then it receives an ID field via UART0.

register

UART0

(Enables Synch Break detection interrupt), SFIE bit = 1 (Enables Synch Field measurement

completed interrupt)

Typical Operation when Receiving a Header Field

1

0

1

0

1

0

1

0

1

0

1

0

Page 362 of 501

(1)

Set by writing 1 to

the LSTART bit in

the LINCR register

Synch Break

(2)

(3)

Measure this period

Set by writing 1 to

the B1CLR bit in

the LINST register

Cleared to 0 upon

acceptance of

interrupt request or

by a program

Synch Field

(4)

(5)

Set by writing 1 to the

B0CLR bit in the LINST

register

Cleared to 0 when Synch

Field measurement

finishes

IDENTIFIER

17. Hardware LIN

(6)

Related parts for R5F21238DFP#U0

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: