IPR-FIR Altera, IPR-FIR Datasheet - Page 32

IPR-FIR

Manufacturer Part Number

IPR-FIR

Description

IP CORE Renewal Of IP-FIR

Manufacturer

Altera

Type

MegaCorer

Specifications of IPR-FIR

Software Application

IP CORE, DSP Filters And Transforms

Supported Families

Arria GX, Arria II GX, Cyclone, HardCopy, Stratix

Core Architecture

FPGA

Core Sub-architecture

Arria, Cyclone, Stratix

Rohs Compliant

NA

Function

Finite Impulse Response Compiler

License

Renewal License

Lead Free Status / RoHS Status

na

Lead Free Status / RoHS Status

na

3–8

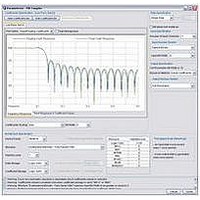

Analyzing the Coefficients

FIR Compiler User Guide

1

1

The FIR Compiler contains a coefficient analysis tool, which you can use to create sets

of coefficients and perform actions on each set.

Some actions, such as scaling, apply to all sets. Other actions, such as recreating,

reloading, or deleting, apply to the set you are currently viewing.

The FIR Compiler supports up to 16 sets of coefficients. You can switch between sets

using the coefficient tabs in the Parameterize - FIR Compiler page. (The coefficient

sets are numbered, for example, Low Pass Set 1, Low Pass Set 2 and so on.)

When you select a set, the frequency response of the floating-point coefficients is

displayed in blue, and the frequency response of the fixed-point coefficients in green.

You can also view the actual coefficient values. by clicking the Time Response &

Coefficient Values tab.

The FIR Compiler supports two’s complement, signed binary fractional notation,

which allows you to monitor which bits are preserved and which bits are removed

during filtering. A signed binary fractional number has the format:

A signed binary fractional number is interpreted as shown below:

If, for example, the number has 3 fractional bits and 4 integer bits plus a sign bit, the

entire 8-bit integer number is divided by 8, which yields a number with a binary

fractional component.

DSP Builder incorporates the sign bit as part of the integer bits. Thus, if you are using

the FIR filter in a DSP Builder design, DSP builder will recognize the sign bit as an

additional integer bit.

When converted to decimal numbers, certain fractions have an infinite number of

binary bits. For example, converting 1/3 to a decimal number yields 0.333n with n

representing an infinite number of 3s. Similarly, numbers such as 1/10 cannot be

represented in a finite number of binary digits with full precision. If you use signed

binary fractional notation, the FIR Compiler uses the fractional number that most

closely matches the original number for the number of bits of precision you select.

For this tutorial, select Auto for Coefficients Scaling and 12 for the Coefficient Bit

Width.

Auto scaling (without the power of two option) provides the maximum signal-to-

noise ratio. All other scaling factors such as Signed Binary Fractional can result in a

loss of effective bits (that is, where each effective bit provides 6dB of SNR).

<sign> <integer bits>.<fractional bits>

<sign> <x

<sign> <x

<sign> <i integer bits>.<y

<sign> <x

where i = ceil(log

1

2

3

integer bits>.<y

integer bits>.<y

integer bits>.<y

2

(number of coefficients)) + x

1

2

3

+ y

1

fractional bits>

fractional bits>

fractional bits>

2

fractional bits>

Original input data

Original coefficient data

Full precision after FIR calculation

Output data after limiting precision

1

+ x

2

© December 2010 Altera Corporation

Chapter 3: Parameter Settings

Analyzing the Coefficients