IPR-FIR Altera, IPR-FIR Datasheet - Page 35

IPR-FIR

Manufacturer Part Number

IPR-FIR

Description

IP CORE Renewal Of IP-FIR

Manufacturer

Altera

Type

MegaCorer

Specifications of IPR-FIR

Software Application

IP CORE, DSP Filters And Transforms

Supported Families

Arria GX, Arria II GX, Cyclone, HardCopy, Stratix

Core Architecture

FPGA

Core Sub-architecture

Arria, Cyclone, Stratix

Rohs Compliant

NA

Function

Finite Impulse Response Compiler

License

Renewal License

Lead Free Status / RoHS Status

na

Lead Free Status / RoHS Status

na

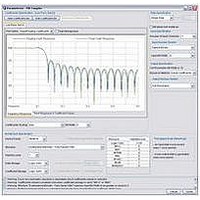

Chapter 3: Parameter Settings

Specify the Architecture Specification

Specify the Architecture Specification

Table 3–3. Architecture Trade-Offs

© December 2010 Altera Corporation

Distributed

arithmetic

Distributed

arithmetic

Distributed

arithmetic

DSP block

multiplier

Available

option for all

architectures

Technology

1

Fully parallel Large area

Fully serial

Multibit

serial

Multicycle

Pipelining

Option

When adjusting the input and output specification, follow these tips:

■

■

You are now ready to select the architecture parameters from the lower half of the

Parameterize - FIR Compiler page.

The FIR Compiler supports several filter structures, including:

■

■

■

■

For maximum clock speed, select the Distributed Arithmetic: Fully Serial Filter

structure. (For Stratix, Stratix II, Stratix III, or Stratix IV devices, using smaller

memory resources for coefficient and data storage is faster than using larger memory

resources.) For maximum throughput, select the Distributed Arithmetic: Fully Parallel

structure.

When reloading coefficients, a multicycle variable FIR filter structure has a short

reloading time compared to a fixed FIR filter. Additionally, smaller memory blocks

have a shorter reloading time than larger memory blocks.

Table 3–3

For more information about the filter architectures and how they operate, refer to

“FIR Compiler” on page

Truncating from the MSB reduces logic resources more than saturation.

The Number of Input Channels option is useful for designs such as modulators

and demodulators, which have I and Q channels. If you are designing this type of

application, select 2 input channels. This tutorial uses the default settings.

Variable/Fixed coefficient: Multicycle

Distributed arithmetic: Fully Parallel Filter

Distributed arithmetic: Fully Serial Filter

Distributed arithmetic: Multibit Serial Filter

Small area

Medium area

Area depends on the number

of calculation cycles selected

(area increases as the number

of calculation cycles increases)

Creates a higher performance

filter with an area increase.

describes the relative trade-offs for the different architecture options.

Area

4–1.

Creates a fast filter: 140 to over 300 MSPS throughput with

pipelining in Stratix II devices.

Requires multiple clock cycles for a single computation.

Uses several serial units to increase throughput.This results

in greater throughput than fully serial, but less throughput

than fully parallel.

Data throughput increases as the number of calculation

cycles decreases. This architecture takes advantage of

Stratix, Stratix II, Stratix III, or Stratix IV DSP Blocks, and

Cyclone II Multipliers.

Increases throughput with additional latency and size

increase.

Speed (Data Throughput)

FIR Compiler User Guide

3–11