DK86064-2 Fujitsu Semiconductor America Inc, DK86064-2 Datasheet - Page 16

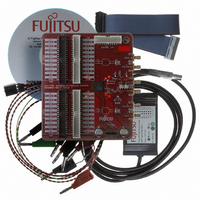

DK86064-2

Manufacturer Part Number

DK86064-2

Description

KIT DEB DUAL 14BIT DAC MB86064

Manufacturer

Fujitsu Semiconductor America Inc

Specifications of DK86064-2

Number Of Dac's

2

Number Of Bits

14

Outputs And Type

1, Differential

Sampling Rate (per Second)

1G

Data Interface

Serial

Dac Type

Current

Voltage Supply Source

Analog and Digital

Operating Temperature

-40°C ~ 85°C

Utilized Ic / Part

MB86064

For Use With

865-1111 - DAC DK FPGA ADAPTER BOARD865-1012 - KIT DEV DUAL 14BIT MB86064 SMA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

865-1010

1.7

Pin X_RESET is the device reset pin. On the falling edge of X_RESET the device is reset and all

registers are set to their default values. After a reset most parts of the device are powered down. See

Table 11, DAC Core Register POWER DOWN. Power to each internal block may be individually

controlled through this register.

Examples of typical settings are:

• 0x0000B80

• 0x0001580

• 0x0000180

All are based on both the divided clock outputs and loop-clocks being enabled.

Page 16 of 52

Disclaimer : The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before

POWER DOWN

Reset and Power Down

ordering.The information and circuit diagrams in this document are presented “as is”, no license is granted by implication or otherwise.

(bit)

The DAC control register bits, pdn_daca & pdn_dacb, must be set in conjunction with the

DAC CONFIG register bits to ensure the correct internal reference current is used. See

section 1.3.

10

12

11

0

1

2

3

4

5

6

7

8

9

DAC A enabled for LVDS data

DAC B enabled for LVDS data

Both DACs enabled for LVDS data

Table 11: DAC Core Register: POWER DOWN [0x1C3]

pdn_ckandrefs

pdn_loopcks

pdn_outcks

pdn_indatb

pdn_indata

pdn_reg18

pdn_reg25

pdn_odatb

pdn_odata

pdn_regck

pdn_reglo

pdn_dacb

pdn_daca

Label

Production

Low voltage (~1.1V) regulator control

0 = Enabled (default) , 1 = Powered down

1.8V clock regulator control

0 = Enabled (default) , 1 = Powered down

1.8V DAC regulator control

0 = Enabled (default) , 1 = Powered down

2.5V bandgap regulator control

0 = Enabled (default) , 1 = Powered down

DAC common circuit (clocks, references and bias) control

0 = All enabled (default) , 1 = All powered down

Divided output clocks

0 = Enabled (default) , 1 = Powered down

Loop clocks

0 = Enabled, 1 = Powered down (default)

Access to TEST output pin by DAC B

0 = Enabled, 1 = Disabled (default)

Access to TEST output pin by DAC A

0 = Enabled, 1 = Disabled (default)

DAC B data input power down control

0 = Enabled, 1 = Powered down (default)

DAC A data input power down control

0 = Enabled, 1 = Powered down (default)

DAC B control

0 = Enabled, 1 = Powered down (default)

DAC A control

0 = Enabled, 1 = Powered down (default)

Copyright © 2004-2005 Fujitsu Microelectronics Europe GmbH

MB86064 Dual 14-bit 1GSa/s DAC

Function

October 2005 Version 1.2

N.B. See note below

N.B. See note below

FME/MS/DAC80/DS/4972