AT91SAM7X256B-CU Atmel, AT91SAM7X256B-CU Datasheet - Page 281

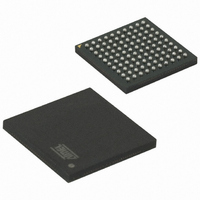

AT91SAM7X256B-CU

Manufacturer Part Number

AT91SAM7X256B-CU

Description

IC MCU 256KB FLASH 100TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7X256B-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

64K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

91S

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

64 KB

Interface Type

CAN, Ethernet, SPI, I2S, TWI, USART, USB

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Package

100TFBGA

Device Core

ARM7TDMI

Family Name

91S

Maximum Speed

55 MHz

On-chip Adc

8-chx10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 281 of 687

- Download datasheet (11Mb)

29. Two-wire Interface (TWI)

29.1

29.2

6120H–ATARM–17-Feb-09

Overview

Block Diagram

The Two-wire Interface (TWI) interconnects components on a unique two-wire bus, made up of

one clock line and one data line with speeds of up to 400 Kbits per second, based on a byte-ori-

ented transfer format. It can be used with any Atmel Two-wire Interface bus Serial EEPROM and

I²C compatible device such as Real Time Clock (RTC), Dot Matrix/Graphic LCD Controllers and

Temperature Sensor, to name but a few. The TWI is programmable as master transmitter or

master receiver with sequential or single-byte access. A configurable baud rate generator per-

mits the output data rate to be adapted to a wide range of core clock frequencies. Below,

29-1

Table 29-1.

Notes:

Figure 29-1. Block Diagram

I2C Standard

Standard Mode Speed (100 KHz)

Fast Mode Speed (400 KHz)

7 or 10 bits Slave Addressing

START BYTE

Repeated Start (Sr) Condition

ACK and NACK Management

Slope control and input filtering (Fast mode)

Clock strectching

lists the compatibility level of the Atmel Two-wire Interface and a full I2C compatible device.

1. START + b000000001 + Ack + Sr

2. A repeated start condition is only supported in Master Receiver mode. See

”Internal Address” on page 286

(1)

Atmel TWI compatibility with i2C Standard

PMC

APB Bridge

MCK

AT91SAM7X512/256/128 Preliminary

Two-wire

Interface

Atmel TWI

Supported

Supported

Supported

Not Supported

Not Fully Supported

Supported

Not Supported

Supported

Interrupt

TWI

PIO

AIC

(2)

TWCK

TWD

Section 29.5.5

Table

281

Related parts for AT91SAM7X256B-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU 32BIT 128K 64LQFP

Manufacturer:

Atmel

Datasheet: