AT91SAM7X256B-CU Atmel, AT91SAM7X256B-CU Datasheet - Page 521

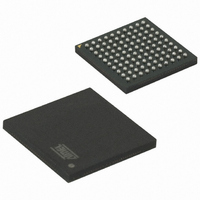

AT91SAM7X256B-CU

Manufacturer Part Number

AT91SAM7X256B-CU

Description

IC MCU 256KB FLASH 100TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7X256B-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

64K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

91S

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

64 KB

Interface Type

CAN, Ethernet, SPI, I2S, TWI, USART, USB

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Package

100TFBGA

Device Core

ARM7TDMI

Family Name

91S

Maximum Speed

55 MHz

On-chip Adc

8-chx10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 521 of 687

- Download datasheet (11Mb)

36.7.2

6120H–ATARM–17-Feb-09

CAN Controller Interrupt Handling

Figure 36-10. Possible Initialization Procedure

There are two different types of interrupts. One type of interrupt is a message-object related

interrupt, the other is a system interrupt that handles errors or system-related interrupt sources.

All interrupt sources can be masked by writing the corresponding field in the CAN_IDR register.

They can be unmasked by writing to the CAN_IER register. After a power-up reset, all interrupt

sources are disabled (masked). The current mask status can be checked by reading the

CAN_IMR register.

The CAN_SR register gives all interrupt source states.

The following events may initiate one of the two interrupts:

• Message object interrupt

• System interrupts

– Data registers in the mailbox object are available to the application. In Receive

– A sent transmission was aborted.

– Bus off interrupt: The CAN module enters the bus off state.

– Error passive interrupt: The CAN module enters Error Passive Mode.

– Error Active Mode: The CAN module is neither in Error Passive Mode nor in Bus Off

Mode, a new message was received. In Transmit Mode, a message was transmitted

successfully.

mode.

AT91SAM7X512/256/128 Preliminary

Configure a Mailbox in Reception Mode

Enable CAN Controller Interrupt Line

(ABM == 1 and CANEN == 1)

Enable CAN Controller Clock

(CAN_SR or CAN_MSRx)

ABM = 0 and CANEN = 0

CANEN = 1 (ABM == 0)

Change CAN_BR value

End of Initialization

Errors ?

(PMC)

(AIC)

No

Yes

521

Related parts for AT91SAM7X256B-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU 32BIT 128K 64LQFP

Manufacturer:

Atmel

Datasheet: