AT91SAM7X256B-CU Atmel, AT91SAM7X256B-CU Datasheet - Page 583

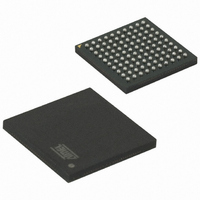

AT91SAM7X256B-CU

Manufacturer Part Number

AT91SAM7X256B-CU

Description

IC MCU 256KB FLASH 100TFBGA

Manufacturer

Atmel

Series

AT91SAMr

Specifications of AT91SAM7X256B-CU

Core Processor

ARM7

Core Size

16/32-Bit

Speed

55MHz

Connectivity

CAN, Ethernet, I²C, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

64K x 8

Voltage - Supply (vcc/vdd)

1.65 V ~ 1.95 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-TFBGA

Processor Series

91S

Core

ARM7TDMI

Data Bus Width

32 bit

Data Ram Size

64 KB

Interface Type

CAN, Ethernet, SPI, I2S, TWI, USART, USB

Maximum Clock Frequency

55 MHz

Number Of Programmable I/os

62

Number Of Timers

3

Operating Supply Voltage

3.3 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

Operating Temperature Range

- 40 C to + 85 C

Package

100TFBGA

Device Core

ARM7TDMI

Family Name

91S

Maximum Speed

55 MHz

On-chip Adc

8-chx10-bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 583 of 687

- Download datasheet (11Mb)

• CLK: MDC clock divider

Set according to system clock speed. This determines by what number system clock is divided to generate MDC.

For conformance with 802.3, MDC must not exceed 2.5MHz (MDC is only active during MDIO read and write operations).

• RTY: Retry test

Must be set to zero for normal operation. If set to one, the back off between collisions is always one slot time. Setting this

bit to one helps testing the too many retries condition. Also used in the pause frame tests to reduce the pause counters

decrement time from 512 bit times, to every rx_clk cycle.

• PAE: Pause Enable

When set, transmission pauses when a valid pause frame is received.

• RBOF: Receive Buffer Offset

Indicates the number of bytes by which the received data is offset from the start of the first receive buffer.

• RLCE: Receive Length field Checking Enable

When set, frames with measured lengths shorter than their length fields are discarded. Frames containing a type ID in

bytes 13 and 14 — length/type ID = 0600 — are not be counted as length errors.

• DRFCS: Discard Receive FCS

When set, the FCS field of received frames are not be copied to memory.

• EFRHD:

Enable Frames to be received in half-duplex mode while transmitting.

• IRXFCS: Ignore RX FCS

When set, frames with FCS/CRC errors are not rejected and no FCS error statistics are counted. For normal operation, this

bit must be set to 0.

6120H–ATARM–17-Feb-09

RBOF

CLK

00

01

10

11

00

01

10

11

MDC

MCK divided by 8 (MCK up to 20 MHz)

MCK divided by 16 (MCK up to 40 MHz)

MCK divided by 32 (MCK up to 80 MHz)

MCK divided by 64 (MCK up to 160 MHz)

Offset

No offset from start of receive buffer

One-byte offset from start of receive buffer

Two-byte offset from start of receive buffer

Three-byte offset from start of receive buffer

AT91SAM7X512/256/128 Preliminary

583

Related parts for AT91SAM7X256B-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR AT91SAM7X256/128

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU, MPU & DSP Development Tools KICKSTART KIT ATMEL AT91SAM7X

Manufacturer:

IAR Systems

Part Number:

Description:

MCU ARM9 64K SRAM 144-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU FLASH 256K 100LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MPU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 ULTRA LOW PWR 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM9 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU ARM9 SAMPLING 217CBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 217-LFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 208-PQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-LQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ARM 512K HS FLASH 100-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM9 MCU 200 MHZ 324-TFBGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM MCU 16BIT 128K 256BGA

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC ARM7 MCU 32BIT 128K 64LQFP

Manufacturer:

Atmel

Datasheet: