M30879FLGP#U3 Renesas Electronics America, M30879FLGP#U3 Datasheet - Page 180

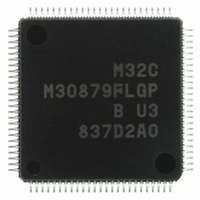

M30879FLGP#U3

Manufacturer Part Number

M30879FLGP#U3

Description

IC M32C/87 MCU FLASH 100LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M32C/80r

Specifications of M30879FLGP#U3

Core Size

16/32-Bit

Program Memory Size

1MB (1M x 8)

Core Processor

M32C/80

Speed

32MHz

Connectivity

CAN, EBI/EMI, I²C, IEBus, IrDA, SIO, UART/USART

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

85

Program Memory Type

FLASH

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 26x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LQFP

Controller Family/series

M32C

No. Of I/o's

85

Ram Memory Size

48KB

Cpu Speed

32MHz

No. Of Timers

2

Digital Ic Case Style

LQFP

Embedded Interface Type

CAN, I2C, UART

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

R0K330879S001BE - KIT DEV RSK M32C/87R0K330879S000BE - KIT DEV RSK M32C/87

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30879FLGP#U3M30879FLGP#U5

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 180 of 629

- Download datasheet (16Mb)

M32C/87 Group (M32C/87, M32C/87A, M32C/87B)

REJ09B0180-0151 Rev.1.51 Jul 31, 2008

Page 156 of 587

14.4

14.3.2

14.3.3

14.4.1

14.4.2

14.4.3

In DMACII, a single transfer, burst transfer, and multiple transfer are available. The BRST bit in MOD selects

either a single transfer or burst transfer, and the MULT bit in MOD selects a multiple transfer. COUNT determines

how many transfers occur. No transfer occurs when COUNT is set to 0000h.

DMACII transfers immediate data to a given memory location. A fixed or incremented address can be selected

as a destination address. Store immediate data into SADR. To transfer an 8-bit immediate data, write data in the

low-order byte of SADR. (The high-order byte is ignored.)

After two memory data, or an immediate data and a memory data, are added together, DMACII transfers the

calculated result to a given memory location. Set a memory address or immediate data to be calculated in

SADR. Set another memory address to be calculated in OADR. To use a “memory + memory” calculation

transfer, a fixed or incremented address can be selected as a source or destination address. If a source address is

incremented, an operation address also becomes incremented. To use an “immediate data + memory”

calculation transfer, a fixed or incremented address can be selected as a destination address.

For one transfer request, DMACII transfers an 8-bit or 16-bit data once. When an incremented address is

selected for a source or destination address, DMACII increments the address after every transfer for the

following transfer.

COUNT is decremented every time a transfer occurs. If using the end-of-transfer interrupt, an interrupt occurs

when COUNT reaches zero.

For one transfer request, DMACII continuously transfers data the number of times determined by COUNT.

COUNT is decremented every time DMACII transfers one transfer unit, and when it reaches zero, a burst

transfer is completed. If using the end-of-transfer interrupt, an interrupt occurs at the end of the burst transfer.

While the burst transfer is taking place, no interrupt can be acknowledged.

When using the multiple transfer, select the memory-to-memory transfer. For one transfer request, DMACII

transfers data multiple times. Bits CNT2 to CNT0 in MOD selects the number of transfers from 001b (once) to

111b (7 times). Do not set bits CNT2 to CNT0 to 000b.

Source and destination addresses enough for all transfers must be allocated alternately in addresses following

MOD and COUNT in DMACII index.

While the transfers are taking place the number of times set using bits CNT2 to CNT0, no interrupt can be

acknowledged. When the multiple transfer is selected, a calculation transfer, burst transfer, chain transfer, and

end-of-transfer interrupt cannot be used.

Transfer Modes

Immediate Data Transfer

Calculation Transfer

Single Transfer

Burst Transfer

Multiple Transfer

14. DMACII

Related parts for M30879FLGP#U3

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: