M30879FLGP#U3 Renesas Electronics America, M30879FLGP#U3 Datasheet - Page 380

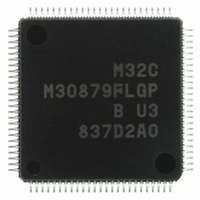

M30879FLGP#U3

Manufacturer Part Number

M30879FLGP#U3

Description

IC M32C/87 MCU FLASH 100LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M32C/80r

Specifications of M30879FLGP#U3

Core Size

16/32-Bit

Program Memory Size

1MB (1M x 8)

Core Processor

M32C/80

Speed

32MHz

Connectivity

CAN, EBI/EMI, I²C, IEBus, IrDA, SIO, UART/USART

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

85

Program Memory Type

FLASH

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 26x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LQFP

Controller Family/series

M32C

No. Of I/o's

85

Ram Memory Size

48KB

Cpu Speed

32MHz

No. Of Timers

2

Digital Ic Case Style

LQFP

Embedded Interface Type

CAN, I2C, UART

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

R0K330879S001BE - KIT DEV RSK M32C/87R0K330879S000BE - KIT DEV RSK M32C/87

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30879FLGP#U3M30879FLGP#U5

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 380 of 629

- Download datasheet (16Mb)

M32C/87 Group (M32C/87, M32C/87A, M32C/87B)

REJ09B0180-0151 Rev.1.51 Jul 31, 2008

Page 356 of 587

22.3.2

Table 22.8

Waveform generation channel

OUTCi_ j pin

Output waveform

Waveform output start condition

Waveform output stop condition

Interrupt request generation timing An interrupt request is generated at the second clock cycle after the base timer

Selectable function

Output level from the OUTCi_j pin is inverted every time the base timer value matches the GiPOj register value

(i = 1, 2; j = 0 to 7).

Table 22.8 lists specifications of phase-delayed waveform output mode. Figure 22.28 shows an example of

phase-delayed waveform output mode operation.

Phase-Delayed Waveform Output Mode (Group 1 and Group 2)

Item

Phase-Delayed Waveform Output Mode Specifications

Group 1 and 2: channels 0 to 7

Pulse output

• Base timer is not reset:

• Base timer is reset when base timer value matches the GiPO0 register value:

Set both the BTS bit in the GiBCR1 register and the IFEj bit in the GiFE register

to 1

Set either the BTS or IFEj bit to 0

value matches the GiPOj register value.

• Initial value set function:

• Inverted output function:

The POijR bit in the IIOkIR register (k = 0 to 11) becomes 1 (interrupt requested)

when an interrupt request is generated.

Cycle:

“H” and “L” widths:

Cycle:

“H” and “L” widths:

(See Figure 11.18 IIO0IR to IIO11IR Registers)

-Bits UD1 and UD0 in G1BCR1 register are set to 00b (counter increment

mode)

-Bits UD1 and UD0 in G1BCR1 register are set to 00b (counter increment mode)

Set the initial output level when waveform output is started (determined by the

IVL bit in the GiPOCRj register)

Output the inverted waveform level (determined by the INV bit in the GiPOCRj

register)

p: setting value of the GiPO0 register (0001h to FFFDh)

If GiPOq register value (q = 1 to 7) (0000h to FFFFh) ≥ p + 2, the output level

is not inverted

65536 × 2

2 (p + 2)

65536

p + 2

fBTi

fBTi

fBTi

fBTi

22. Intelligent I/O (Waveform Generation Function)

Specification

Related parts for M30879FLGP#U3

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: