M30879FLGP#U3 Renesas Electronics America, M30879FLGP#U3 Datasheet - Page 362

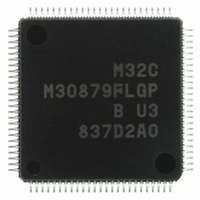

M30879FLGP#U3

Manufacturer Part Number

M30879FLGP#U3

Description

IC M32C/87 MCU FLASH 100LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M32C/80r

Specifications of M30879FLGP#U3

Core Size

16/32-Bit

Program Memory Size

1MB (1M x 8)

Core Processor

M32C/80

Speed

32MHz

Connectivity

CAN, EBI/EMI, I²C, IEBus, IrDA, SIO, UART/USART

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

85

Program Memory Type

FLASH

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 26x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LQFP

Controller Family/series

M32C

No. Of I/o's

85

Ram Memory Size

48KB

Cpu Speed

32MHz

No. Of Timers

2

Digital Ic Case Style

LQFP

Embedded Interface Type

CAN, I2C, UART

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

R0K330879S001BE - KIT DEV RSK M32C/87R0K330879S000BE - KIT DEV RSK M32C/87

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30879FLGP#U3M30879FLGP#U5

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 362 of 629

- Download datasheet (16Mb)

M32C/87 Group (M32C/87, M32C/87A, M32C/87B)

REJ09B0180-0151 Rev.1.51 Jul 31, 2008

Page 338 of 587

Figure 22.15

(1) Group 1

(2) Group 2

Reset signal by matching

Reset signal by matching

communication function

Two phase pulse input

i = 1, 2

BCK1 and BCK0, IT: Bits in the GiBCR0 register

RST1, RST2, BTS: Bits in the GiBCR1 register

RST0: Bit in the G2BCR1 register

BTRE: Bit in the G1POCR0 register

BT1S, BT2S: Bits in the BTSR register

NOTE:

the INT0 or INT1 pin

the G1PO0 register

the G2PO0 register

1. The divider is reset when both the BTiS and BTS bits are set to 0.

the base timer with

the base timer with

group 1 base timer

Reset signal from

"L" is applied to

Request from

Base Timer Block Diagram

f1

BT1S

BT2S

BTS

BTS

BCK1 and BCK0

f1

11

BCK1 and BCK0

RST1

RST2

RST0

RST1

RST2

11

10

Divider 2(n+1)

Divider 2(n+1)

(Note 1)

(Note 1)

Base timer reset

Base timer reset

fBT1

fBT2

Base Timer

Base Timer

b0 to b13

b9

b14 b15

b14 b15

0

1

BTRE

22. Intelligent I/O (Base Timer)

1

0

0

1

Overflow signal

Overflow signal

IT

IT

Base timer

Base timer

interrupt request

interrupt request

Related parts for M30879FLGP#U3

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: