M30879FLGP#U3 Renesas Electronics America, M30879FLGP#U3 Datasheet - Page 199

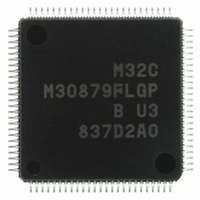

M30879FLGP#U3

Manufacturer Part Number

M30879FLGP#U3

Description

IC M32C/87 MCU FLASH 100LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M32C/80r

Specifications of M30879FLGP#U3

Core Size

16/32-Bit

Program Memory Size

1MB (1M x 8)

Core Processor

M32C/80

Speed

32MHz

Connectivity

CAN, EBI/EMI, I²C, IEBus, IrDA, SIO, UART/USART

Peripherals

DMA, POR, PWM, WDT

Number Of I /o

85

Program Memory Type

FLASH

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 26x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LQFP

Controller Family/series

M32C

No. Of I/o's

85

Ram Memory Size

48KB

Cpu Speed

32MHz

No. Of Timers

2

Digital Ic Case Style

LQFP

Embedded Interface Type

CAN, I2C, UART

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

R0K330879S001BE - KIT DEV RSK M32C/87R0K330879S000BE - KIT DEV RSK M32C/87

Eeprom Size

-

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30879FLGP#U3M30879FLGP#U5

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 199 of 629

- Download datasheet (16Mb)

M32C/87 Group (M32C/87, M32C/87A, M32C/87B)

REJ09B0180-0151 Rev.1.51 Jul 31, 2008

Page 175 of 587

Figure 15.15

Contents of the counter

n = contents of the reload

Input to TAiIN pin

TAiS bit in the

TABSR register

TAiUD bit in the

UDF register

IR bit in the TAiIC

register

(Conditions) TAiMR register: Bits TMOD1 and TMOD0 are set to 01b (event counter mode)

i = 0 to 4

register

Operation in Event Counter Mode When Not Handling Two-Phase Pulse Signals

FFFFh

0000h

“H”

“L”

1

0

1

0

1

0

n

The MR1 bit is set to 1 (rising edges of an external signal counted)

The MR2 bit is set to 0 (UDF register setting)

Bits TCK1 to TCK0 bit are set to 00b (reload)

Count starts

Reload

Underflow

Decrement to increment

Set to 1 by a program

Set to 0 by an interrupt request acknowledgement or

Count stops

Count resumes

by a program

Overflow

Reload

15. Timer A

Related parts for M30879FLGP#U3

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: