Chameleon-PIC Nurve Networks, Chameleon-PIC Datasheet - Page 160

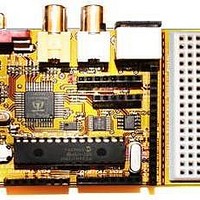

Chameleon-PIC

Manufacturer Part Number

Chameleon-PIC

Description

MCU, MPU & DSP Development Tools PIC24 & PROPELLER DEV SYSTEM (SBC)

Manufacturer

Nurve Networks

Datasheet

1.CHAMELEON-PIC.pdf

(263 pages)

Specifications of Chameleon-PIC

Processor To Be Evaluated

PIC24

Data Bus Width

16 bit

Interface Type

USB, VGA, PS/2, I2C, ISP, SPI

Operating Supply Voltage

3.3 V, 5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 160 of 263

- Download datasheet (12Mb)

© 2009 NURVE NETWORKS LLC “Exploring the Chameleon PIC 16-Bit”

open drain design where SDA and SCL can only be pulled down by the master, and SDA alone by the slave. Then

2

addressing is achieved by a 7-bit address sent down the I

C bus to all devices, only the listening device with the

matching address responds and communication begin. Let’s discuss this process more in detail.

2

19.2.1 Understanding I

C Bus States

2

The I

C protocol is rather complex compared to SPI protocol. In fact, there is no “SPI protocol” per se. SPI is a simple

serial packet much like RS-232. The only “protocol” that SPI devices have are inherent in the devices themselves and

2

what the bytes sent and received mean. I

C on the other hand has this very complex arbitration system to handle

2

multiple Masters on the bus, this is facilitated via the electrical design as well as a “state machine” that I

C is based on.

2

Considering this, I

C is rather complex. We are only briefly going to cover some of the high level concepts of the protocol

and its primary states; START, and STOP.

To begin with, data is transfer is always initiated by a Master device (remember Slaves can only respond to Masters). A

high to low transition on the SDA line while SCL is high is defined to be a “START condition” or a “repeated START

2

condition”. Everything begins with the “START” condition, that’s the first thing to remember with I

C. Figure 19.5 below

show the timing waveforms for this event.

2

Figure 19.5 – Timing waveforms for I

C “START Condition”.

A START condition is always followed by the (unique) 7-bit slave address along with a single bit signifying the “Data

Direction” either read or write. The Slave device addressed acknowledges the Master by holding SDA low for one clock

cycle. If the Master does not receive an acknowledgement the transfer is terminated. Depending of the Data Direction

bit, the Master or Slave now transmits 8-bits of data on the SDA line. The receiving device then acknowledges the data.

Figure 19.6 shows what happens during data transmission following the initial START and addressing phases.

Figure 19.6 – Timing waveforms for I2C data transmission.

Multiple bytes can be transferred in one direction before a repeated START or a STOP condition is issued by the Master.

The transfer is terminated when the Master issues a “STOP condition”. A STOP condition is defined by a low to high

transition on the SDA line while the SCL is high. Confusing isn’t it?

If a Slave device cannot handle incoming data until it has performed some other function, it can hold SCL low to force the

2

Master into a “wait-state” for as long as it needs to. All data packets transmitted on the I

C bus are 9 bits long, consisting

of 8 data bits, and an acknowledge bit. Now, during a data transfer, the Master generates the clock and the START and

160

Related parts for Chameleon-PIC

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MCU, MPU & DSP Development Tools AVR8 VIDEO GAME DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Part Number:

Description:

MCU, MPU & DSP Development Tools PIC24 VIDEO GAME DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Part Number:

Description:

MCU, MPU & DSP Development Tools AVR8 & PROPELLER DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Datasheet: