Chameleon-PIC Nurve Networks, Chameleon-PIC Datasheet - Page 44

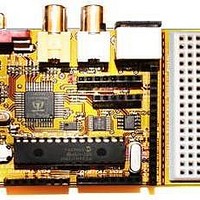

Chameleon-PIC

Manufacturer Part Number

Chameleon-PIC

Description

MCU, MPU & DSP Development Tools PIC24 & PROPELLER DEV SYSTEM (SBC)

Manufacturer

Nurve Networks

Datasheet

1.CHAMELEON-PIC.pdf

(263 pages)

Specifications of Chameleon-PIC

Processor To Be Evaluated

PIC24

Data Bus Width

16 bit

Interface Type

USB, VGA, PS/2, I2C, ISP, SPI

Operating Supply Voltage

3.3 V, 5 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 44 of 263

- Download datasheet (12Mb)

10.3.1 VGA Horizontal Timing

Referring to Figure 10.3(b), each of the 480 lines of video are composed of the following standard named regions:

As you can see even the names are similar to NTSC. However, unlike NSTC, VGA is very unforgiving you must follow the

spec more closely otherwise the monitor’s will typically ignore the signal. The next interesting thing is that all the signals

are riding on different lines. For example, the hsync and vsync both have their own signal lines, and the R,G, and B

signals do as well, so it’s much easier to generate all the signals in a large state machine and then route them to the

output ports as a single byte wide stream of data.

Therefore, to generate a line of video (with a negative sync polarity), you start by turning off all the R, G, B channels with a

0.0V, and simply hold the hsync line LOW for 3.77 μs (B), then you wait 1.89 μs (C) and the VGA is ready to take R, G, B

data, now you clock out 640 pixels at 25.175 MHz for a total time of 25.17 μs (D) for the active video portion. You then

turn the video lines R, G, B off, and wait 0.94 μs (E) and then start the process again. And that’s all there is too it. Perform

this process 480 times then it’s time for a vertical sync and retrace, let’s look at that.

10.3.2 VGA Vertical Timing

The vertical sync and retrace is much easier than the horizontal timing since there is no video to interleave in the signal.

Referring to Figure 10.3 (c) the various named timing regions of the vertical timing are:

O (16.68 ms)

P (64 μs)

Q (1.02 ms)

R (15.25 ms)

S (0.35 ms)

The meaning of each is similar to that in the horizontal sync period, except the “event” they are focused around are the

480 lines of active video, so the 480 lines are encapsulated in (R). The most important thing to realize is that these times

are in measured in milliseconds for the most part except for the Vsync pulse. So once again, the timing of an entire frame

starts off with the Vsync pulse (P) for 64 μs, after which comes the back porch (Q) for 1.02 ms, followed by the active

video (R) for 15.25 ms. During the active video you don’t need to worry about the Vsync line since you would be

generating 480 lines of video, when complete, back to the Vsync timing region (S) the front porch for 0.35 ms and then the

frame is complete.

The thing to remember is that unlike composite video, a VGA signal needs to be driven by multiple signals for each of the

constituent controls; R, G, B, Hsync, and VSync which in my opinion is much easier than modulating and mixing them all

together as in NTSC which is a blood bath of crosstalk and noise! Now, that we have the horizontal and vertical timing for

VGA covered, let’s review the actual video data portion of the signal during the active video and see what that’s all about.

A (31.77 μs)

B (3.77 μs)

C (1.89 μs)

D (25.17 μs)

E (0.94 μs)

NOTE

TIP

Total frame time

Vsync pulse.

Back porch

Active video time.

Front porch.

Even though, VGA is 640x480 that doesn’t mean that you have to put out 640x480

pixels and stream video at that rate. The Propeller chip for example only has 32K bytes

of memory, thus a full frame buffer with one byte per pixel would require 307,200 bytes!

Therefore, the idea is to use tile graphics modes, or reduced resolution modes, but still

conforming to the VGA timing constraints.

You might be wondering where the 25.175 MHz clock is generated on the Chameleon?

Well, the Propeller chip is generating the signal and it has internal counters and PLLs

that generate the 25.175 MHz signal for us.

Scanline time.

HSync pulse.

Back porch.

Active video time.

Front porch.

© 2009 NURVE NETWORKS LLC “Exploring the Chameleon PIC 16-Bit”

44

Related parts for Chameleon-PIC

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

MCU, MPU & DSP Development Tools AVR8 VIDEO GAME DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Part Number:

Description:

MCU, MPU & DSP Development Tools PIC24 VIDEO GAME DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Part Number:

Description:

MCU, MPU & DSP Development Tools AVR8 & PROPELLER DEV SYSTEM (SBC)

Manufacturer:

Nurve Networks

Datasheet: