SI1000-C-GM Silicon Laboratories Inc, SI1000-C-GM Datasheet - Page 153

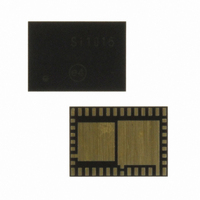

SI1000-C-GM

Manufacturer Part Number

SI1000-C-GM

Description

IC TXRX MCU + EZRADIOPRO

Manufacturer

Silicon Laboratories Inc

Specifications of SI1000-C-GM

Package / Case

42-QFN

Frequency

240MHz ~ 960MHz

Data Rate - Maximum

256kbps

Modulation Or Protocol

FSK, GFSK, OOK

Applications

General Purpose

Power - Output

20dBm

Sensitivity

-121dBm

Voltage - Supply

1.8 V ~ 3.6 V

Current - Receiving

18.5mA

Current - Transmitting

85mA

Data Interface

PCB, Surface Mount

Memory Size

64kB Flash, 4kB RAM

Antenna Connector

PCB, Surface Mount

Number Of Receivers

1

Number Of Transmitters

1

Wireless Frequency

240 MHz to 960 MHz

Interface Type

UART, SMBus, SPI, PCA

Output Power

20 dBm

Operating Supply Voltage

0.9 V to 3.6 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Maximum Supply Current

4.1 mA

Minimum Operating Temperature

- 40 C

Modulation

FSK, GFSK, OOK

Protocol Supported

C2, SMBus

Core

8051

Program Memory Type

Flash

Program Memory Size

64 KB

Data Ram Size

4352 B

Supply Current (max)

4.1 mA

Cpu Family

Si100x

Device Core

8051

Device Core Size

8b

Frequency (max)

25MHz

Total Internal Ram Size

4.25KB

# I/os (max)

22

Number Of Timers - General Purpose

4

Operating Supply Voltage (typ)

2.5/3.3V

Operating Supply Voltage (max)

3.6V

Operating Supply Voltage (min)

1.8V

On-chip Adc

18-chx10-bit

Instruction Set Architecture

CISC

Mounting

Surface Mount

Pin Count

42

Package Type

QFN EP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Operating Temperature

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1881-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SI1000-C-GM

Manufacturer:

FSC

Quantity:

1 000

- Current page: 153 of 376

- Download datasheet (3Mb)

14.2. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon

as the instruction that sets the bit completes execution. All internal registers and memory maintain their

original data. All analog and digital peripherals can remain active during Idle mode.

Note: To ensure the MCU enters a low power state upon entry into Idle Mode, the one-shot circuit should be

Idle mode is terminated when an enabled interrupt is asserted or a reset occurs. The assertion of an

enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU to resume

operation. The pending interrupt will be serviced and the next instruction to be executed after the return

from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit.

If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence

and begins program execution at address 0x0000.

If enabled, the Watchdog Timer (WDT) will eventually cause an internal watchdog reset and thereby termi-

nate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event

of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by

software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This pro-

vides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefi-

nitely, waiting for an external stimulus to wake up the system. Refer to Section “18.6. PCA Watchdog Timer

Reset” on page 180 for more information on the use and configuration of the WDT.

14.3. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruc-

tion that sets the bit completes execution. In Stop mode the precision internal oscillator and CPU are

stopped; the state of the low power oscillator and the external oscillator circuit is not affected. Each analog

peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop

Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs

the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode.

The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the

MCD timeout of 100 µs.

Stop Mode is a legacy 8051 power mode; it will not result in optimal power savings. Sleep or Suspend

mode will provide more power savings if the MCU needs to be inactive for a long period of time.

On Si1000/1/2/3/4/5 devices, the Precision Oscillator Bias is not automatically disabled and should be dis-

abled by software to achieve the lowest possible Stop mode current.

To ensure the MCU enters a low power state upon entry into Stop Mode, the one-shot circuit should be

enabled by clearing the BYPASS bit (FLSCL.6) to logic 0. See the note in SFR Definition 13.3. FLSCL: Flash

Scale for more information on how to properly clear the BYPASS bit.

enabled by clearing the BYPASS bit (FLSCL.6) to logic 0. See the note in SFR Definition 13.3. FLSCL:

Flash Scale for more information on how to properly clear the BYPASS bit.

Rev. 1.0

Si1000/1/2/3/4/5

153

Related parts for SI1000-C-GM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

QFN 42/I�/915 MHZ, SNAP ENABLED PROGRAMABLE XCVR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

QFN 42/I�/64KB, 4KB RAM, +20 DBM, PROGRAMMABLE XCVR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Microcontrollers (MCU) 915MHz SNAP enabled program XCVR

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

BOARD EVALUATION FOR SI1000

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

BOARD EVALUATION FOR SI1000

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

BOARD EVALUATION FOR SI1012

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

BOARD EVALUATION FOR SI1002

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

DEVELOPMENT KIT SI101X

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

BOARD EVALUATION FOR SI1004

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

BOARD EVALUATION FOR SI1004

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

BOARD EVALUATION FOR SI1012

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

BOARD EVALUATION FOR SI1014

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

DEVELOPMENT KIT SI101X

Manufacturer:

Silicon Laboratories Inc

Datasheet: