EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 543

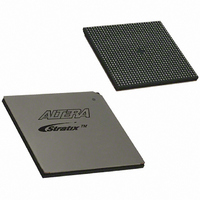

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 543 of 864

- Download datasheet (11Mb)

Figure 5–44. LVDS x2 Mode Schematic Using DDR I/O Circuitry

Altera Corporation

July 2005

rx_inclk

RXp

RXn

datain[0]

inclock

inclock

RX_PLL

DDIO In

dataout_h[0]

dataout_l[0]

The transmitter output clock requires extra DDR output circuitry that has

the input high and input low connected to V

output clock frequency is the same as the input frequency of the DDR

output circuitry.

Other Modes

For other modes, you can still to use the DDR circuitry for better

frequency performance. You can use either the LEs or the M512 RAM

block for the deserialization.

M512 RAM Block as Serializer/Deserializer Interface

In addition to using the DDR circuitry and the M512 RAM block, you

need two extra counters per memory block to provide the address for the

memory: a fast counter powering up at 0 and a slow counter powering up

at 2. The M512 RAM block is configured as a simple dual-port memory

block, where the read enable and the write enable signals are always tied

high.

bypass receiver and SERDES bypass transmitter, respectively.

/1 clock1

/2 clock0

Figures 5–45

Custom Logic

and

High-Speed Differential I/O Interfaces in Stratix Devices

5–46

show the block diagram for the SERDES

GND

V

CC

datain_h[0]

datain_l[0]

outclock

datain_h[0]

datain_l[0]

outclock

Stratix Device Handbook, Volume 2

DDIO Out

DDIO Out

CC

and GND respectively. The

dataout[0]

dataout[0]

TXp

TXn

tx_outclk

5–71

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: