EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 690

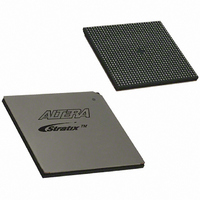

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 690 of 864

- Download datasheet (11Mb)

General Architecture

10–6

Stratix Device Handbook, Volume 2

Note to

(1)

Blocks

Logic

Pins

Architectural

Table 10–3. Stratix & Stratix GX Location Assignment Syntax

Elements

You can make assignments to I/O pads using IOC_X<number>_Y<number>_N<number>.

(1)

Table

10–3:

LAB, DSP,

DSPOUT, M512,

M4K, M-RAM

LE, IOC, PLL,

DSPMULT,

SERDESTX,

SERDESRX

I/O pins

Element Name

Table 10–3

Stratix GX devices.

Use the following guidelines with the new naming system:

■

■

■

■

■

Figure 10–2

numbering convention.

Quartus II software.

The anchor point, or origin, in Stratix and Stratix GX devices is in the

bottom-left corner, instead of the top-left corner as in APEX II and

APEX 20K devices.

The anchor point, or origin, of a large block element (e.g., a M-RAM

or DSP block) is also the bottom-left corner.

All numbers are zero-based, meaning the origin at the bottom-left of

the device is X0, Y0.

The I/O pins constitute the first and last rows and columns in the

X-Y coordinates. Therefore, the bottom row of pins resides in

X<number>, Y0, and the first left column of pins resides in X0,

Y<number>.

The sub-location of elements, N, numbering begins at the top.

Therefore, the LEs in an LAB are still numbered from top to bottom,

but start at zero.

<element_name>

_Y

<element_name>

_Y

pin_

<number>

<number>

highlights the new location syntax used for Stratix and

<pin_label>

show the Stratix and Stratix GX architectural element

Location Syntax

_N

<number>

_X

_X

Figure 10–3

<number>

<number>

LAB_X1_Y1

LC_X1_Y1_N0

pin_5

displays the floorplan view in the

Location

Example of Location Syntax

Designates the LAB in

row 1, column 1

Designates the first

LE, N0, in the LAB

located in row 1,

column 1

Pin 5

Altera Corporation

Description

July 2005

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: