EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 647

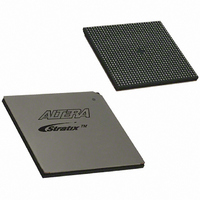

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 647 of 864

- Download datasheet (11Mb)

Altera Corporation

July 2005

The Ethernet PHY (layer 1 of the OSI model) connects the media (optical

or copper) to the MAC (layer 2). The Ethernet architecture further divides

the PHY (layer 1) into a PMD sublayer, a PMA sublayer, and a PCS. For

example, optical transceivers are PMD sublayers. The PMA converts the

data between the PMD sublayer and the PCS sublayer. The PCS is made

up of coding (e.g., 8b/10b, 64b/66b) and serializer or multiplexing

functions.

how Altera implements certain blocks and interfaces.

10-Gigabit Ethernet has three different implementations for the PHY:

10GBASE-X, 10GBASE-R, and 10GBASE-W. The 10GBASE-X

implementation is a PHY that supports the XAUI interface. The XAUI

interface used in conjunction with the XGMII extender sublayer (XGXS)

allows more separation in distance between the MAC and PHY.

10GBASE-X PCS uses four lanes of 8b/10b coded data at a rate of

3.125 Gbps. 10GBASE-X is a wide wave division multiplexing (WWDM)

LAN PHY. 10GBASE-R and 10GBASE-W are serial LAN PHYs and serial

WAN PHYs, respectively. Unlike 10GBASE-X, 10GBASE-R and

10GBASE-W implementations have a XSBI interface and are described in

more detail in the following section.

Implementing 10-Gigabit Ethernet Using Stratix & Stratix GX Devices

Figure 8–2

shows the components of 10-Gigabit Ethernet and

Stratix Device Handbook, Volume 2

8–3

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: