EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 725

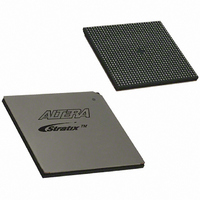

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 725 of 864

- Download datasheet (11Mb)

Altera

Configuration

Devices

Configuration

Schemes

Altera Corporation

July 2005

f

f

different number of padding bits during programming. However, for any

specific version of the Quartus II software, any design targeted for the

same device has the same configuration file size.

The Altera enhanced configuration devices (EPC16, EPC8, and EPC4

devices) support a single-device configuration solution for high-density

FPGAs and can be used in the FPP and PS configuration schemes. They

are ISP-capable through its JTAG interface. The enhanced configuration

devices are divided into two major blocks, the controller and the flash

memory.

For information on enhanced configuration devices, see the Enhanced

Configuration Devices (EPC4, EPC8 & EPC16) Data Sheet and the Using

Altera Enhanced Configuration Devices chapter in the Configuration

Handbook.

The EPC2 and EPC1 configuration devices provide configuration support

for the PS configuration scheme. The EPC2 device is ISP-capable through

its JTAG interface. The EPC2 and EPC1 can be cascaded to hold large

configuration files.

For more information on EPC2, EPC1, and EPC1441 configuration

devices, see the Configuration Devices for SRAM-Based LUT Devices Data

Sheet.

This section describes how to configure Stratix and Stratix GX devices

with the following configuration schemes:

■

■

■

■

■

■

■

PS Configuration

PS configuration of Stratix and Stratix GX devices can be performed using

an intelligent host, such as a MAX

memory, an Altera configuration device, or a download cable. In the PS

scheme, an external host (MAX device, embedded processor,

configuration device, or host PC) controls configuration. Configuration

data is clocked into the target Stratix devices via the DATA0 pin at each

rising edge of DCLK.

PS Configuration with Configuration Devices

PS Configuration with a Download Cable

PS Configuration with a Microprocessor

FPP Configuration

PPA Configuration

JTAG Programming & Configuration

JTAG Programming & Configuration of Multiple Devices

Configuring Stratix & Stratix GX Devices

®

device, microprocessor with flash

Stratix Device Handbook, Volume 2

11–7

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: