EP1S40B956C5 Altera, EP1S40B956C5 Datasheet - Page 745

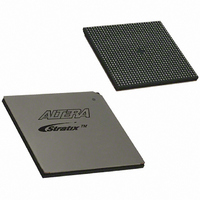

EP1S40B956C5

Manufacturer Part Number

EP1S40B956C5

Description

IC STRATIX FPGA 40K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S40B956C5

Number Of Logic Elements/cells

41250

Number Of Labs/clbs

4125

Total Ram Bits

3423744

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S40B956C5

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

- Current page: 745 of 864

- Download datasheet (11Mb)

Altera Corporation

July 2005

Figure 11–12. Parallel Configuration Using a Microprocessor

Note to

(1)

For multi-device parallel configuration with a microprocessor, the nCEO

pin of the first Stratix or Stratix GX device is cascaded to the second

device’s nCE pin. The second device in the chain begins configuration

within one clock cycle; therefore, the transfer of data destinations is

transparent to the microprocessor. Because the CONF_DONE pins of the

devices are connected together, all devices initialize and enter user mode

at the same time.

Because the nSTATUS pins are also tied together, if any of the devices

detects an error, the entire chain halts configuration and drives nSTATUS

low. The microprocessor can then pulse nCONFIG low to restart

configuration. If the Auto-restart configuration after error option is on,

the Stratix and Stratix GX devices release nSTATUS after a reset time-out

period. The microprocessor can then reconfigure the devices once

nSTATUS is released.

using a microprocessor.

when both Stratix and Stratix GX devices are receiving the same data. In

this case, the microprocessor sends the data to both devices

simultaneously, and the devices configure simultaneously.

Microprocessor

The pull-up resistors should be connected to any V

level input voltage (V

ADDR DATA[7..0]

Figure

Memory

11–12:

Figure 11–13

IH

) specification.

Figure 11–14

Configuring Stratix & Stratix GX Devices

shows multi-device configuration

V

CC

10 kΩ

shows multi-device configuration

(1)

Stratix Device Handbook, Volume 2

GND

V

CC

10 kΩ

(1)

CC

that meets the Stratix high-

CONF_DONE

nSTATUS

nCE

DATA[7..0]

nCONFIG

DCLK

Stratix Device

MSEL2

MSEL1

MSEL0

nCEO

GND

11–27

N.C.

Related parts for EP1S40B956C5

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: