DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 193

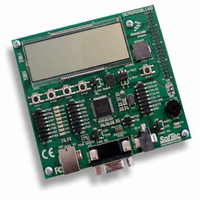

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 193 of 360

- Download datasheet (4Mb)

10.6.4

In this example, the FLL will be used (in FEI mode) to multiply the internal 243 kHz (approximate)

reference clock up to 10.8 MHz to achieve 5.4 MHz bus frequency. This system will also use the trim

function to fine tune the frequency based on an external reference signal.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately

8 MHz on ICGOUT which corresponds to a 4 MHz bus frequency (f

The clock scheme will be FLL engaged, internal (FEI). So

Solving for N / R gives:

A trim procedure will be required to hone the frequency to exactly 5.4 MHz. An example of the trim

procedure is shown in example #4.

The values needed in each register to set up the desired operation are:

ICGC1 = $28 (%00101000)

ICGC2 = $31 (%00110001)

ICGS1 = $xx

ICGS2 = $xx

ICGFLTLU/L = $xx

Freescale Semiconductor

Bit 7

Bit 6

Bit 5

Bits 4:3 CLKS

Bit 2

Bit 1

Bit 0

Bit 7

Bit 6:4 MFD

Bit 3

Bit 2:0 RFD

This is read only except for clearing interrupt flag

This is read only; good idea to read this before performing time critical operations

Not used in this example

N / R = 10.8 MHz /(243/7 kHz * 64) = 4.86 ; We can choose N = 10 and R = 2.

Example #3: No External Crystal Connection, 5.4 MHz Bus

Frequency

HGO

RANGE

REFS

OSCSTEN 0

LOCD

LOLRE

LOCRE

f

ICGOUT

0

0

1

01

0

0

0

011 Sets the MFD multiplication factor to 10

0

001 Sets the RFD division factor to ÷2

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

= (f

Configures oscillator for low power

Configures oscillator for low-frequency range; FLL prescale factor is 64

Oscillator using crystal or resonator requested (bit is really a don’t care)

FLL engaged, internal reference clock mode

Disables the oscillator

Loss-of-clock enabled

Unimplemented or reserved, always reads zero

Generates an interrupt request on loss of lock

Generates an interrupt request on loss of clock

IRG

/ 7) * P * N / R ; P = 64, f

IRG

= 243 kHz

Chapter 10 Internal Clock Generator (S08ICGV4)

Bus

).

Eqn. 10-5

Eqn. 10-6

193

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: