DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 254

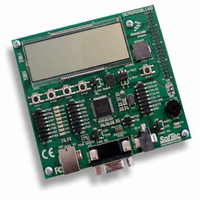

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 254 of 360

- Download datasheet (4Mb)

Chapter 14 Inter-Integrated Circuit (S08IICV1)

254

MULT

Field

ICR

7:6

5:0

IIC Multiplier Factor — The MULT bits define the multiplier factor mul. This factor is used along with the SCL

divider to generate the IIC baud rate. The multiplier factor mul as defined by the MULT bits is provided below.

00 mul = 01

01 mul = 02

10 mul = 04

11 Reserved

IIC Clock Rate — The ICR bits are used to prescale the bus clock for bit rate selection. These bits are used to

define the SCL divider and the SDA hold value. The SCL divider multiplied by the value provided by the MULT

register (multiplier factor mul) is used to generate IIC baud rate.

SDA hold time is the delay from the falling edge of the SCL (IIC clock) to the changing of SDA (IIC data). The

ICR is used to determine the SDA hold value.

Table 14-3

be used to set IIC baud rate and SDA hold time. For example:

Table 14-3

hold value of 9.

If the generated SDA hold value is not acceptable, the MULT bits can be used to change the ICR. This will result

in a different SDA hold value.

IIC baud rate = bus speed (Hz)/(mul * SCL divider)

SDA hold time = bus period (s) * SDA hold value

Bus speed = 8 MHz

MULT is set to 01 (mul = 2)

Desired IIC baud rate = 100 kbps

IIC baud rate = bus speed (Hz)/(mul * SCL divider)

100000 = 8000000/(2*SCL divider)

SCL divider = 40

SDA hold time = bus period (s) * SDA hold value

SDA hold time = 1/8000000 * 9 = 1.125 μs

provides the SCL divider and SDA hold values for corresponding values of the ICR. These values can

shows that ICR must be set to 0B to provide an SCL divider of 40 and that this will result in an SDA

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Table 14-2. IICA Register Field Descriptions

Description

Freescale Semiconductor

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: