DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 71

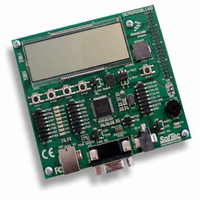

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 71 of 360

- Download datasheet (4Mb)

Freescale Semiconductor

IRQMOD

IRQACK

IRQPE

IRQIE

Field

IRQF

4

3

2

1

0

IRQ Pin Enable — This read/write control bit enables the IRQ pin function. When this bit is set, the IRQ pin can

be used as an interrupt request. Also, when this bit is set, either an internal pull-up or an internal pull-down

resistor is enabled depending on the state of the IRQMOD bit.

0 IRQ pin function is disabled.

1 IRQ pin function is enabled.

IRQ Flag — This read-only status bit indicates when an interrupt request event has occurred.

0 No IRQ request.

1 IRQ event detected.

IRQ Acknowledge — This write-only bit is used to acknowledge interrupt request events (write 1 to clear IRQF).

Writing 0 has no meaning or effect. Reads always return 0. If edge-and-level detection is selected (IRQMOD = 1),

IRQF cannot be cleared while the IRQ pin remains at its asserted level.

IRQ Interrupt Enable — This read/write control bit determines whether IRQ events generate a hardware

interrupt request.

0 Hardware interrupt requests from IRQF disabled (use polling).

1 Hardware interrupt requested whenever IRQF = 1.

IRQ Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level

detection. The IRQEDG control bit determines the polarity of edges and levels that are detected as interrupt

request events. See

0 IRQ event on falling edges or rising edges only.

1 IRQ event on falling edges and low levels or on rising edges and high levels.

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Table 5-3. IRQSC Field Descriptions (continued)

Section 5.5.2.2, “Edge and Level

Description

Sensitivity”

Chapter 5 Resets, Interrupts, and System Configuration

for more details.

71

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: