DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 264

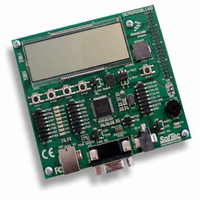

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 264 of 360

- Download datasheet (4Mb)

Chapter 14 Inter-Integrated Circuit (S08IICV1)

14.7

264

1.

2.

3.

4.

1.

2.

3.

4.

5.

6.

7.

Write: IICA

— to set the slave address

Write: IICC

— to enable IIC and interrupts

Initialize RAM variables (IICEN = 1 and IICIE = 1) for transmit data

Initialize RAM variables used to achieve the routine shown in

Write: IICF

— to set the IIC baud rate (example provided in this chapter)

Write: IICC

— to enable IIC and interrupts

Initialize RAM variables (IICEN = 1 and IICIE = 1) for transmit data

Initialize RAM variables used to achieve the routine shown in

Write: IICC

— to enable TX

Write: IICC

— to enable MST (master mode)

Write: IICD

— with the address of the target slave. (The LSB of this byte will determine whether the communication is

The routine shown in

incoming IIC message that contains the proper address will begin IIC communication. For master operation,

communication must be initiated by writing to the IICD register.

Initialization/Application Information

IICC

IICD

IICA

IICS

IICF

master receive or transmit.)

Address to which the module will respond when addressed as a slave (in slave mode)

Data register; Write to transmit IIC data read to read IIC data

Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))

Module configuration

Module status flags

IICEN

TCF

MULT

Figure 14-11

IICIE

IAAS

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Figure 14-10. IIC Module Quick Start

BUSY

MST

Module Initialization (Master)

Module Initialization (Slave)

can handle both master and slave IIC operations. For slave operation, an

Register Model

ARBL

Module Use

TX

ADDR

DATA

TXAK

0

ICR

Figure 14-11

Figure 14-11

RSTA

SRW

IICIF

0

RXAK

0

0

Freescale Semiconductor

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: