DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 257

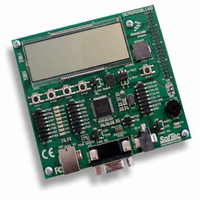

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 257 of 360

- Download datasheet (4Mb)

14.3.4

Freescale Semiconductor

Reset

BUSY

ARBL

RXAK

Field

IAAS

SRW

IICIF

TCF

7

6

5

4

2

1

0

W

R

IIC Status Register (IICS)

TCF

Transfer Complete Flag — This bit is set on the completion of a byte transfer. Note that this bit is only valid

during or immediately following a transfer to the IIC module or from the IIC module.The TCF bit is cleared by

reading the IICD register in receive mode or writing to the IICD in transmit mode.

0 Transfer in progress.

1 Transfer complete.

Addressed as a Slave — The IAAS bit is set when the calling address matches the programmed slave address.

Writing the IICC register clears this bit.

0 Not addressed.

1 Addressed as a slave.

Bus Busy — The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is

set when a START signal is detected and cleared when a STOP signal is detected.

0 Bus is idle.

1 Bus is busy.

Arbitration Lost — This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be

cleared by software, by writing a one to it.

0 Standard bus operation.

1 Loss of arbitration.

Slave Read/Write — When addressed as a slave the SRW bit indicates the value of the R/W command bit of

the calling address sent to the master.

0 Slave receive, master writing to slave.

1 Slave transmit, master reading from slave.

IIC Interrupt Flag — The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by

writing a one to it in the interrupt routine. One of the following events can set the IICIF bit:

0 No interrupt pending.

1 Interrupt pending.

Receive Acknowledge — When the RXAK bit is low, it indicates an acknowledge signal has been received after

the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge

signal is detected.

0 Acknowledge received.

1 No acknowledge received.

1

7

• One byte transfer completes

• Match of slave address to calling address

• Arbitration lost

= Unimplemented or Reserved

IAAS

0

6

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Table 14-5. IICS Register Field Descriptions

Figure 14-6. IIC Status Register (IICS)

BUSY

0

5

ARBL

0

4

Description

3

0

0

Chapter 14 Inter-Integrated Circuit (S08IICV1)

SRW

0

2

IICIF

0

1

RXAK

0

0

257

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: