DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 57

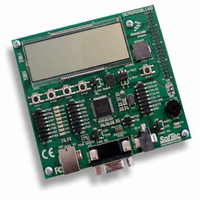

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 57 of 360

- Download datasheet (4Mb)

4.6.2

During reset, the contents of the nonvolatile location NVOPT are copied from FLASH into FOPT. Bits 5

through 2 are not used and always read 0. This register may be read at any time, but writes have no meaning

or effect. To change the value in this register, erase and reprogram the NVOPT location in FLASH memory

as usual and then issue a new MCU reset.

Freescale Semiconductor

SEC0[1:0]

FNORED

200 kHz

150 kHz

20 MHz

10 MHz

Reset

KEYEN

8 MHz

4 MHz

2 MHz

1 MHz

Field

f

Bus

1:0

7

6

W

R

KEYEN

FLASH Options Register (FOPT and NVOPT)

Backdoor Key Mechanism Enable — When this bit is 0, the backdoor key mechanism cannot be used to

disengage security. The backdoor key mechanism is accessible only from user (secured) firmware. BDM

commands cannot be used to write key comparison values that would unlock the backdoor key. For more detailed

information about the backdoor key mechanism, refer to

0 No backdoor key access allowed.

1 If user firmware writes an 8-byte value that matches the nonvolatile backdoor key (NVBACKKEY through

Flash No Redirect (Vector Redirection Disable) — When this bit is 1, then vector redirection is disabled.

0 Vector redirection enabled.

1 Vector redirection disabled.

Security State Code — This 2-bit field determines the security state of the MCU as shown in

the MCU is secure, the contents of RAM and FLASH memory cannot be accessed by instructions from any

unsecured source including the background debug interface. For more detailed information about security, refer

to

7

Section 4.5,

NVBACKKEY+7, in that order), security is temporarily disengaged until the next MCU reset.

(Binary)

PRDIV8

= Unimplemented or Reserved

1

0

0

0

0

0

0

0

FNORED

“Security.”

6

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

This register is loaded from nonvolatile location NVOPT during reset.

Figure 4-6. FLASH Options Register (FOPT)

Table 4-7. FLASH Clock Divider Settings

Table 4-8. FOPT Field Descriptions

0

5

DIV5:DIV0

(Decimal)

12

49

39

19

9

4

0

0

0

4

Description

Section 4.5,

192.3 kHz

0

3

200 kHz

200 kHz

200 kHz

200 kHz

200 kHz

200 kHz

150 kHz

f

FCLK

“Security.”

0

2

Program/Erase Timing Pulse

(5 μs Min, 6.7 μs Max)

SEC01

1

5.2 μs

6.7 μs

5 μs

5 μs

5 μs

5 μs

5 μs

5 μs

Table

Chapter 4 Memory

4-9. When

SEC00

0

57

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: