DEMO9S08LC60 Freescale Semiconductor, DEMO9S08LC60 Datasheet - Page 317

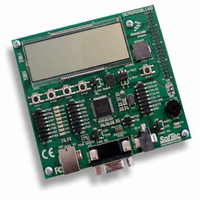

DEMO9S08LC60

Manufacturer Part Number

DEMO9S08LC60

Description

BOARD DEMO FOR 9S08LC60

Manufacturer

Freescale Semiconductor

Type

MCUr

Datasheets

1.DEMO9S08LC60.pdf

(360 pages)

2.DEMO9S08LC60.pdf

(32 pages)

3.DEMO9S08LC60.pdf

(2 pages)

Specifications of DEMO9S08LC60

Contents

Evaluation Board

Processor To Be Evaluated

MC9S08LC60

Interface Type

RS-232, USB

Silicon Manufacturer

Freescale

Core Architecture

HCS08

Core Sub-architecture

HCS08

Silicon Core Number

MC9S08

Silicon Family Name

S08LC

Rohs Compliant

Yes

For Use With/related Products

MC9S08LC60

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 317 of 360

- Download datasheet (4Mb)

1

17.4.3

The debug module includes nine bytes of register space for three 16-bit registers and three 8-bit control

and status registers. These registers are located in the high register space of the normal memory map so

they are accessible to normal application programs. These registers are rarely if ever accessed by normal

user application programs with the possible exception of a ROM patching mechanism that uses the

breakpoint logic.

17.4.3.1

This register contains compare value bits for the high-order eight bits of comparator A. This register is

forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

17.4.3.2

This register contains compare value bits for the low-order eight bits of comparator A. This register is

forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

17.4.3.3

This register contains compare value bits for the high-order eight bits of comparator B. This register is

forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

17.4.3.4

This register contains compare value bits for the low-order eight bits of comparator B. This register is

forced to 0x00 at reset and can be read at any time or written at any time unless ARM = 1.

Freescale Semiconductor

Reset

BDFR is writable only through serial background mode debug commands, not from user programs.

BDFR

Field

W

0

R

DBG Registers and Control Bits

Background Debug Force Reset — A serial active background mode command such as WRITE_BYTE allows

an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot

be written from a user program.

0

0

7

Debug Comparator A High Register (DBGCAH)

Debug Comparator A Low Register (DBGCAL)

Debug Comparator B High Register (DBGCBH)

Debug Comparator B Low Register (DBGCBL)

Figure 17-6. System Background Debug Force Reset Register (SBDFR)

= Unimplemented or Reserved

0

0

6

MC9S08LC60 Series Data Sheet: Technical Data, Rev. 4

Table 17-3. SBDFR Register Field Description

0

0

5

0

0

4

Description

0

0

3

0

0

2

Chapter 17 Development Support

1

0

0

BDFR

0

0

0

1

317

Related parts for DEMO9S08LC60

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: